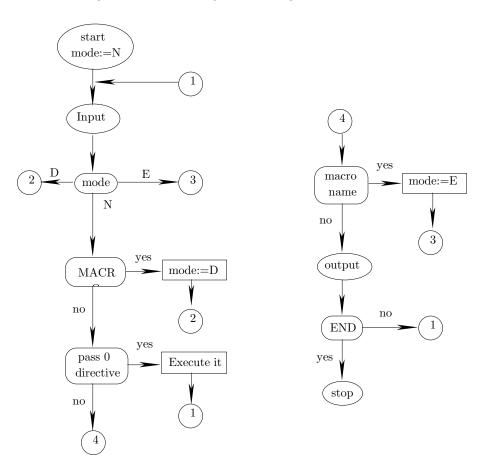

# **Topics in**

# **Computer Organization**

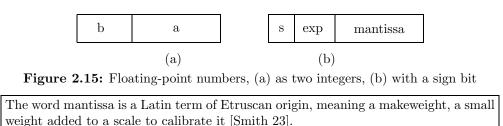

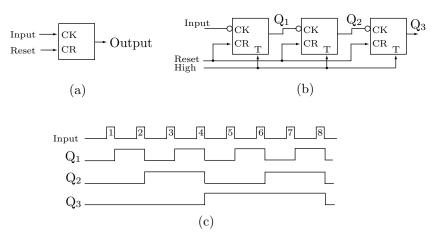

(based on old class notes)

D. Salomon

(619) 443-6528

dsalomon@csun.edu

http://www.davidsalomon.name/

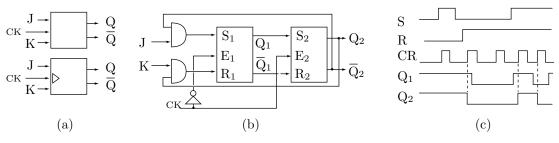

Modern computer programming is a race between programmers striving to write bigger and better idiot-proof programs, and the Universe trying to produce bigger and better idiots. So far, the Universe is winning. —Rich Cook

Feb 2008

# Preface

The dictionary definition of the term "organizing" is "to put together into an orderly, functional, structured whole." This term applies twice to this text because it tries to "put together into an orderly, functional, structured whole" the main components of computers; the way computers are organized.

More and more people use computers, but to most computer users the computer is a "black box," and writing a program is akin to uttering magical incantations. This text tries to clear up these mysteries. It attempts to give the reader a robust framework to which new knowledge can later be added by more studying. Specifically, the text answers the question "how do computers work?" It describes the main components of the computer and their interrelationships. It includes material on the control unit, memory, and input/output processing, as well as topics such as logic devices, microprocessor components, microprogramming, machine instructions, assembly language and assembler operation, and a survey of the main features of some existing computers.

The title of this text is "Computer Organization." This term refers to a conceptual understanding, rather than an engineering understanding, of the inner workings of computers. A more formal definition of this term is "the logical arrangement of the hardware components and how they are interconnected."

Another important term commonly used with computers is "computer architecture." This term answers the question "how is a computer designed?" rather than "how does the computer work?". An alternative definition of computer architecture is "the components or attributes of the computer that are visible to the assembler language programmer."

As a result of these definitions, features such as the instruction set, the word size, addressing modes, and interrupt handling are architectural. Features such as memory technology, bus organization, and handshaking signals are organizational. A typical example is input/output (abbreviated I/O). The I/O instructions in the instruction set are an architectural feature. The physical implementation of those instructions (by way of a DMA device, a channel, or something else) is an organizational feature.

The distinction between organization and architecture can be traced back to 1964. In that year, IBM released its system/360, the first *family* of computers. The different models in the family had different performances (and prices) and, as a result, different organizations. However, they were upward compatible, which means they had the same architecture. The success of the 360 family encouraged IBM and other manufacturers to design many more families of computers, thereby establishing the distinction between organization and architecture.

Here are a few more general terms used with computers.

- "Software" refers to how the computer is used.

- "Hardware" refers to how the computer is constructed (its physical building blocks).

- The general term "computing" refers to problem solving on computers by means of programming.

• The computer itself is a machine that performs tasks and solve problems by storing and manipulating information.

• Information stored in computers is digital (it consists of discrete digits).

#### Preface

These notes are based on experience gained from teaching computer organization over many years. Much of the material found here was originally included in response to questions and requests from students.

The exercises constitute an important part of the notes and should be worked out! The answers are provided, but should be consulted only as a last resort. Remember what the Dodo said:

"Why," said the Dodo, "the best way to explain it is to do it." —Lewis Carroll (1832–1898)

The text is divided into three parts as follows:

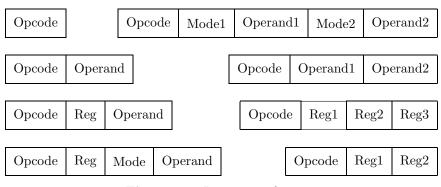

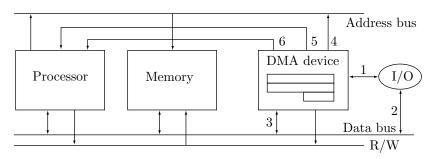

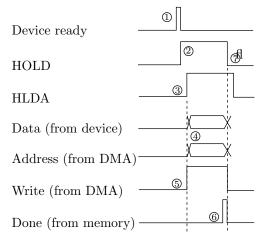

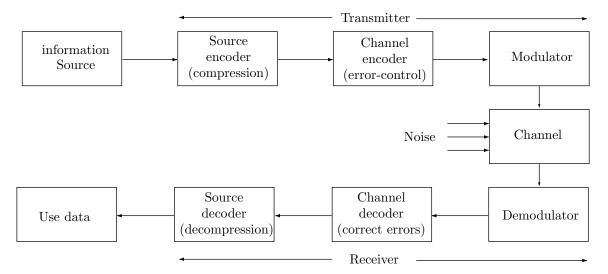

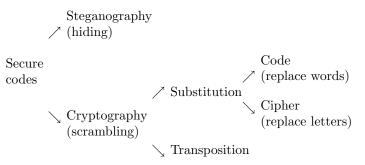

Part I consists of the first six chapters and covers the main concepts of computer organization. Chapter 1 introduces the control unit, instruction fetch and execution, memory, ALU, microprogramming, and interrupts. Chapter 2 is a review of machine instructions and data types. It discusses instruction formats, opcodes, addressing modes, instruction types, floating-point, BCD, and fixed-point numbers, and carry and overflow. Chapter 3 is devoted to the important topic of input/output (I/O). It consists of three parts, the I/O processor, I/O codes, and computer communications. The first part discusses register I/O, memorymapped I/O, DMA, and other types of I/O processors. The second part introduces the ASCII and Unicode codes, continues with a coverage of reliable (i.e., error-detecting and error-correcting) codes, and of data compression methods, and concludes with a description of important cryptographic methods (secure codes). Part three explains serial I/O and how computers are connected in local-area and wide-area networks.

Microprogramming is the topic of chapter 4. The chapter includes a review of the basic concepts and a detailed example of a simple, microprogrammed computer. Parallel computers are discussed in chapter 5. The discussion concentrates on MIMD computers, but SIMD and data flow computers are also mentioned. The short chapter 6 introduces the reader to the concept of reduced instruction-set computers (RISC).

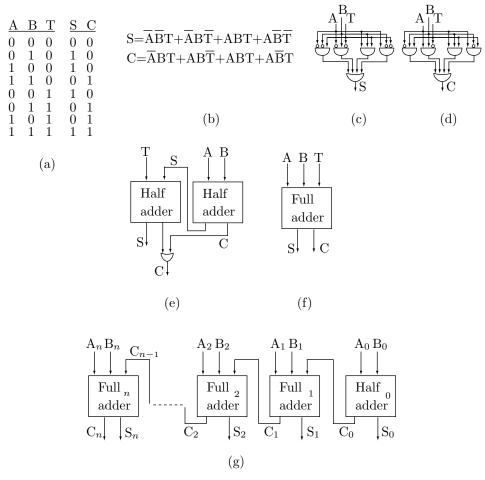

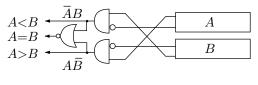

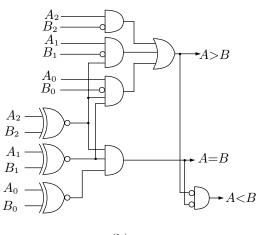

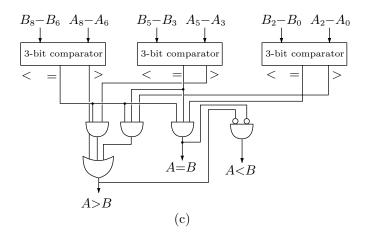

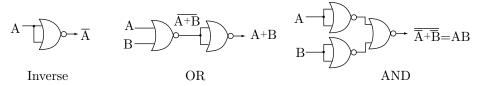

Part II consists of chapters 7 through 9. This is an introduction to digital devices and computer design. Chapter 7 introduces the main digital devices used in computers. It starts with the logic gates and covers latches, counters, decoders, multiplexors, and other devices. Chapter 8 is an introduction to computer memory. The main types of memory and their internal operations are discussed. The ALU and its circuits is the topic of chapter 9. Digital circuits for integer arithmetic, for shifts, and for comparisons are explained in detail.

Part III consists of appendixes that provide information on the history of computers, Unicode, and CD-ROMs.

Hating, as I mortally do, all long unnecessary preface, I shall give you good quarter in this, and use no farther apology, than to prepare you for seeing the loose part of my life, wrote with the same liberty that I led it. —John Cleland, 1749, Fanny Hill

# Contents

|    | Preface              |                                 |    |    |

|----|----------------------|---------------------------------|----|----|

| 1. | Introduction         |                                 |    |    |

|    | 1                    | Terminology                     | 1  |    |

|    | 2                    | The Control Unit                | 2  |    |

|    | 3                    | The Memory                      | 5  |    |

|    | 4                    | Instruction Execution           | 11 |    |

|    | 5                    | CPU Bus Structure               | 17 |    |

|    | 6 Microprogramming   |                                 | 18 |    |

|    | 7                    | Interrupts                      | 20 |    |

|    | 8 I/O Interrupts     |                                 | 26 |    |

|    | 9                    | Interrupts in a Microprocessor  | 28 |    |

|    | 10                   | The ALU                         | 30 |    |

| 2. | Machine Instructions |                                 |    | 33 |

|    | 1                    | Instruction Formats             | 33 |    |

|    | 2                    | The Opcode Size                 | 34 |    |

|    | 3                    | Addressing Modes                | 36 |    |

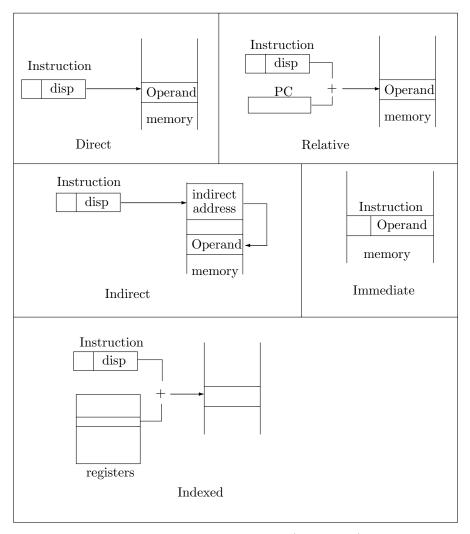

|    | 4                    | The Direct Mode                 | 37 |    |

|    | 5                    | The Relative Mode               | 37 |    |

|    | 6                    | The Immediate Mode              | 38 |    |

|    | 7                    | The Index Mode                  | 38 |    |

|    | 8                    | The Indirect Mode               | 38 |    |

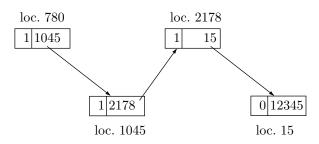

|    | 9                    | Multilevel or Cascaded Indirect | 39 |    |

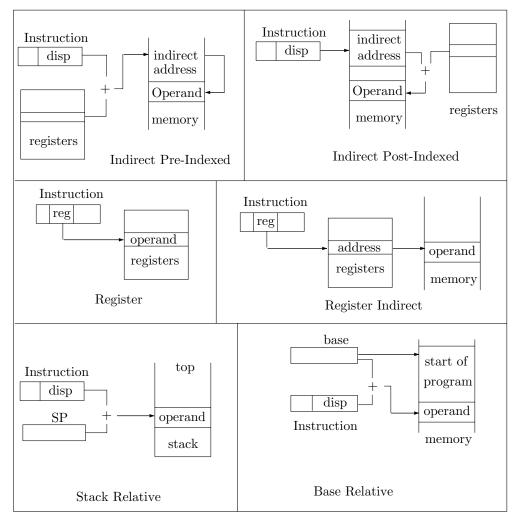

|    | 10                   | Other Addressing Modes          | 40 |    |

|    | 11                   | Instruction Types               | 41 |    |

|    | 12                   | Data Movement Instructions      | 41 |    |

|    | 13                   | Operations                      | 42 |    |

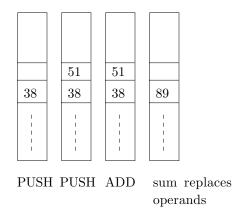

|    | 14                   | N-Operand Instructions          | 48 |    |

|    | 15                   | Actual Instruction Sets         | 48 |    |

|    | 16                   | The VAX Instruction Set         | 49 |    |

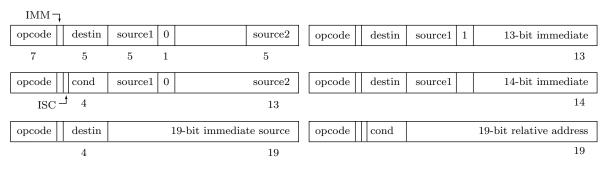

|    | 17                   | The RISC I Instruction Set      | 52 |    |

|    | 18                   | Non-Numeric Data Types          | 53 |    |

|    | 19                   | Numeric Data Types              | 54 |    |

|    | 20                   | Signed Integers                 | 54 |    |

|    | 21                   | Floating-Point Numbers          | 57 |    |

|    | 22                   | Fixed-Point Numbers             | 63 |    |

|    | 23                   | Decimal (BCD) Numbers           | 64 |    |

|    | 24                   | Other BCD Codes                 | 65 |    |

|    | 25                   | Rational Numbers                | 67 |    |

|    | 26                   | Carry and Overflow              | 68 |    |

|           | 1                   | The $I/O$ Processon                        | 71       |  |  |

|-----------|---------------------|--------------------------------------------|----------|--|--|

|           | 1 The I/O Processor |                                            | 71       |  |  |

|           | 2                   | Polled I/O                                 | 73       |  |  |

|           | 3                   | Interrupt I/O                              | 75<br>77 |  |  |

|           | 4                   | DMA                                        | 75       |  |  |

|           | 5                   | I/O Channels                               | 78       |  |  |

|           | 6                   | I/O Codes                                  | 79       |  |  |

|           | 7                   | ASCII and Other Codes                      | 80       |  |  |

|           | 8                   | Information Theory and Algebraic Coding    | 83       |  |  |

|           | 9                   | Error-Detecting and Error-Correcting Codes | 84       |  |  |

|           | 10                  | Data Compression                           | 93       |  |  |

|           | 11                  | Variable-Size Codes                        | 94       |  |  |

|           | 12                  | Huffman Codes                              | 95       |  |  |

|           | 13                  | Facsimile Compression                      | 97       |  |  |

|           | 14                  | Dictionary-Based Methods                   | 100      |  |  |

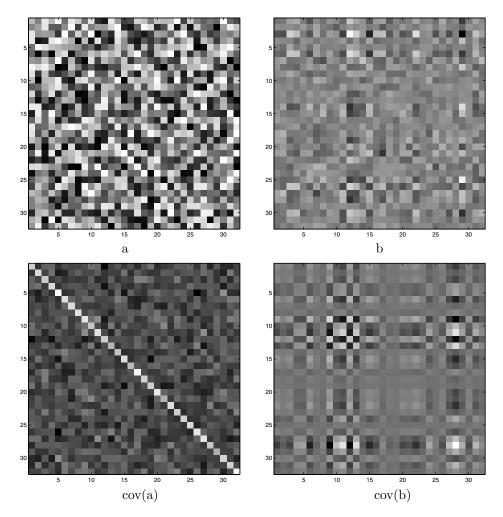

|           | 15                  | Approaches to Image Compression            | 102      |  |  |

|           | 16                  | Secure Codes                               | 107      |  |  |

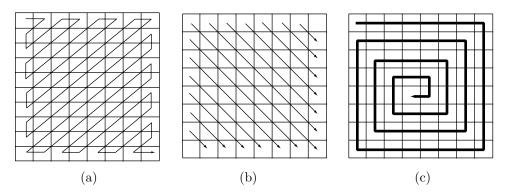

|           | 17                  | Transposition Ciphers                      | 114      |  |  |

| 18        |                     | Transposition by Turning Template          | 116      |  |  |

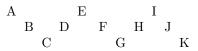

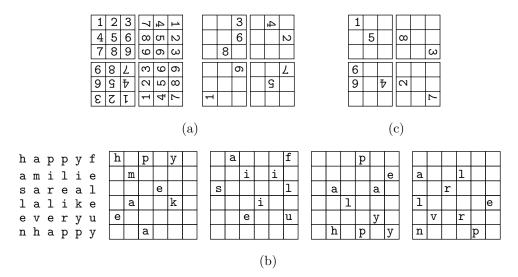

|           | 19                  | Columnar Transposition Cipher              | 118      |  |  |

|           | 20                  | Steganography                              | 126      |  |  |

|           | 21                  | Computer Communications                    | 131      |  |  |

|           | 22                  | Serial I/O                                 | 131      |  |  |

|           | 23                  | Modern Modems                              | 143      |  |  |

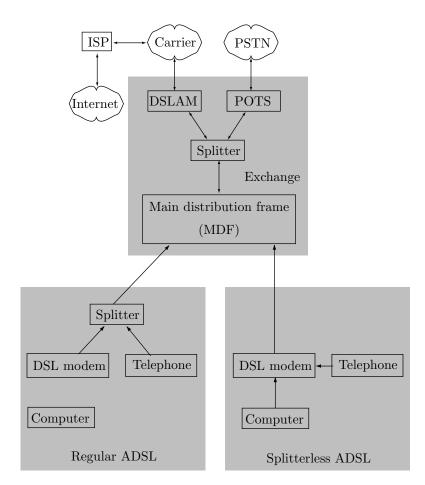

|           | 24                  | ISDN and DSL                               | 144      |  |  |

|           | 25                  | T-1, DS-1 and Their Relatives              | 145      |  |  |

|           | 26                  | Computer Networks                          | 148      |  |  |

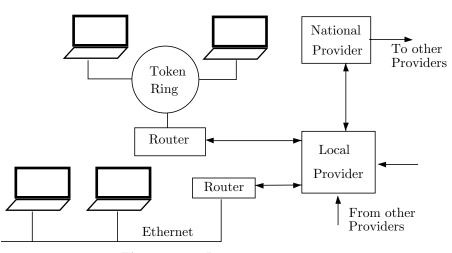

|           | 27                  | Internet Organization                      | 152      |  |  |

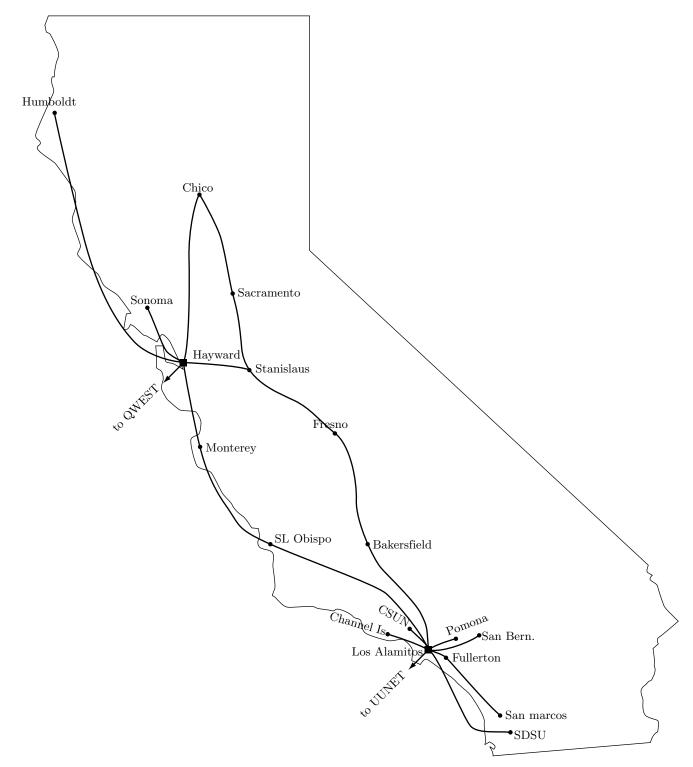

|           | 28                  | Internet: Physical Layout                  | 153      |  |  |

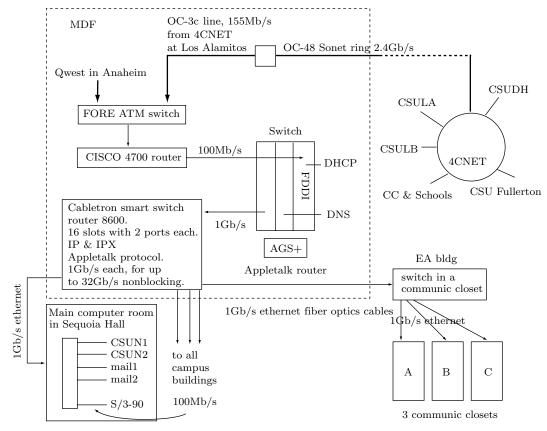

|           | 29                  | CSUN in the Internet                       | 160      |  |  |

|           | 30                  | ICANN and IANA                             | 163      |  |  |

|           | 31                  | The World Wide Web                         | 163      |  |  |

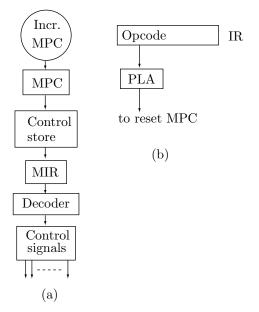

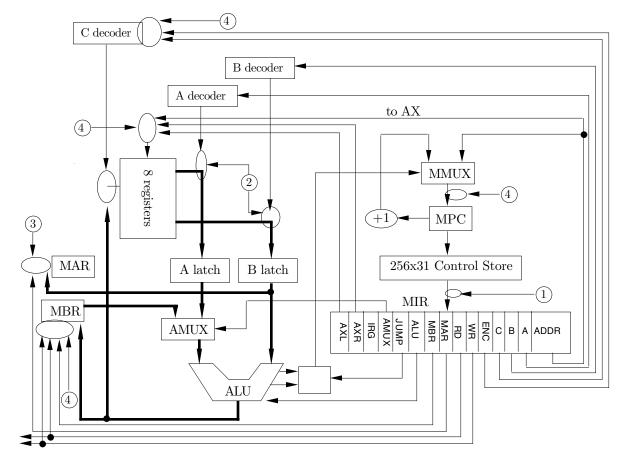

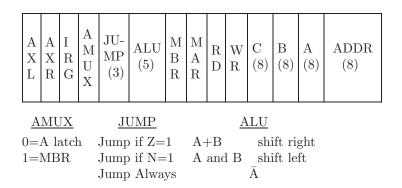

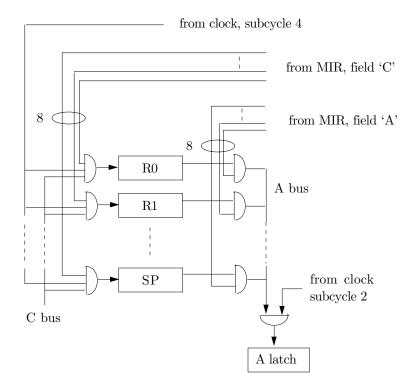

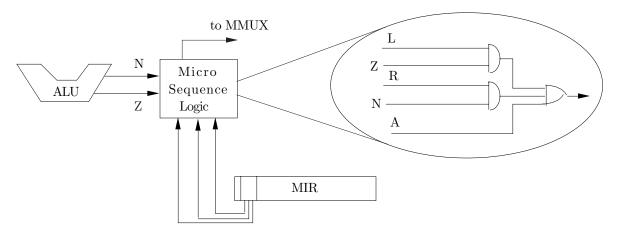

| <b>1.</b> | Mici                | Microprogramming                           |          |  |  |

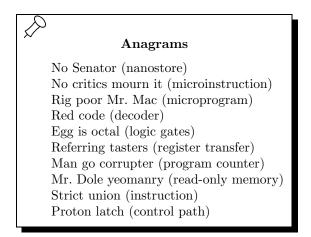

|           | 1                   | Basic Principles                           | 167      |  |  |

|           | 2                   | A Short History of Microprogramming        | 168      |  |  |

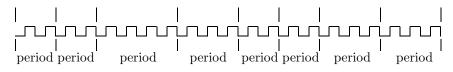

|           | 3                   | The Computer Clock                         | 169      |  |  |

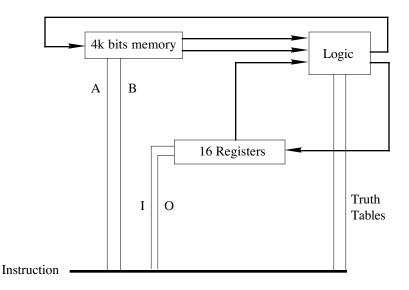

|           | 4                   | An Example Microarchitecture               | 169      |  |  |

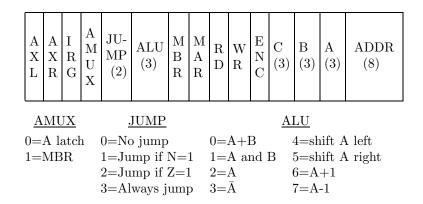

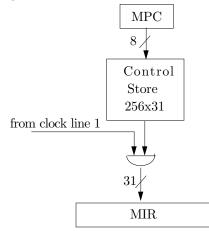

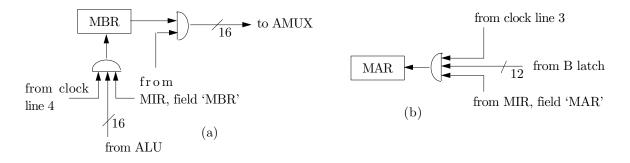

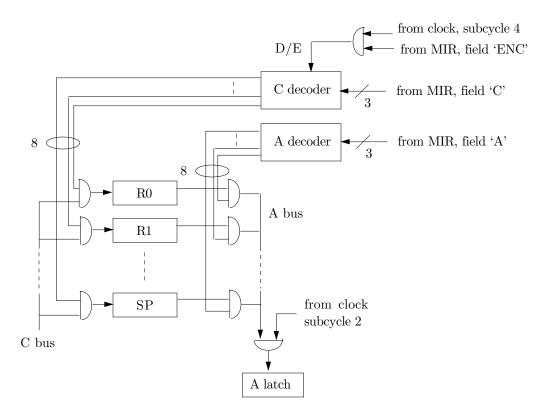

|           | 5                   | The Microinstructions                      | 170      |  |  |

|           | 6                   | Microinstruction Timing                    | 172      |  |  |

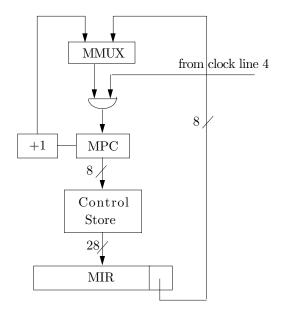

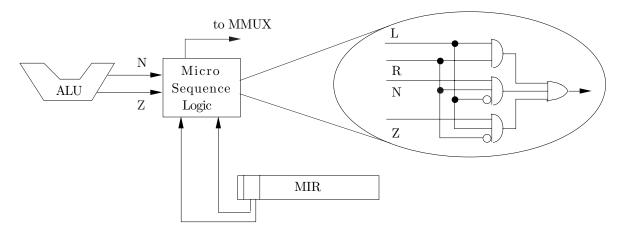

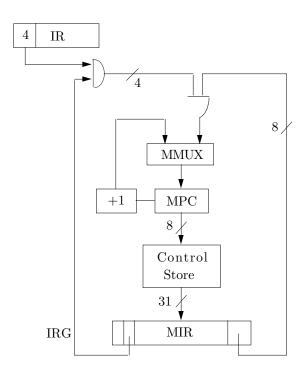

|           | 7                   | The Control Path                           | 175      |  |  |

|           | 8                   | The Machine Instructions                   | 177      |  |  |

|           | 9                   | The Microcode                              | 178      |  |  |

|           | 10                  | Final Notes                                | 184      |  |  |

|           | 11                  | A Horizontal Example                       | 187      |  |  |

|           |                     | 1                                          |          |  |  |

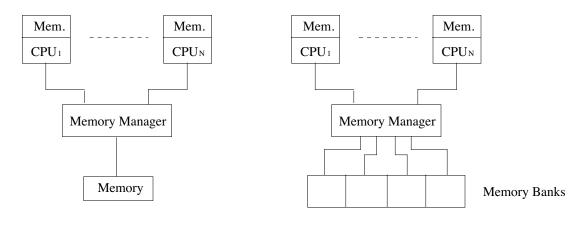

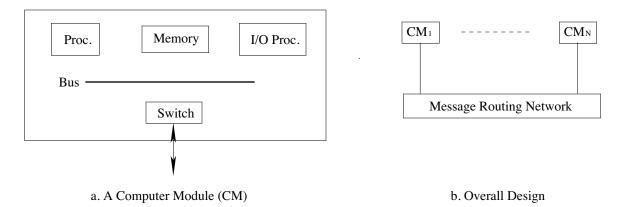

| 5.  | Parallel Computers                                                                                                                 |                                       |     |     |  |

|-----|------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-----|-----|--|

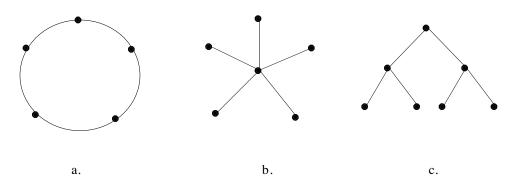

|     | 1                                                                                                                                  | Introduction                          | 189 |     |  |

|     | 2                                                                                                                                  | Classifying Architectures             | 189 |     |  |

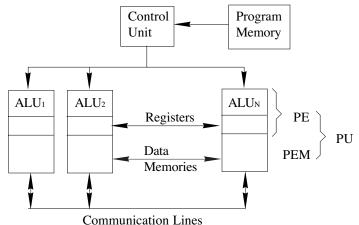

|     | 3                                                                                                                                  | Parallel Processing Methods           | 190 |     |  |

|     | 4                                                                                                                                  | Design Criteria                       | 190 |     |  |

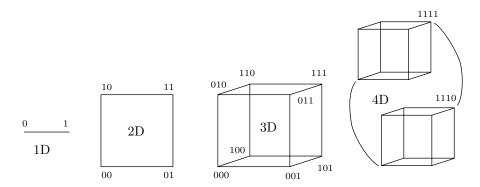

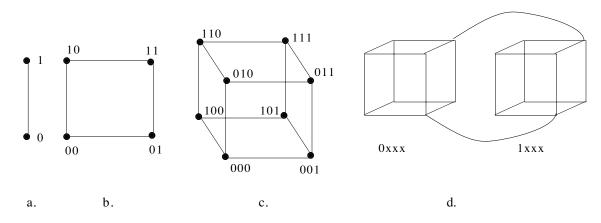

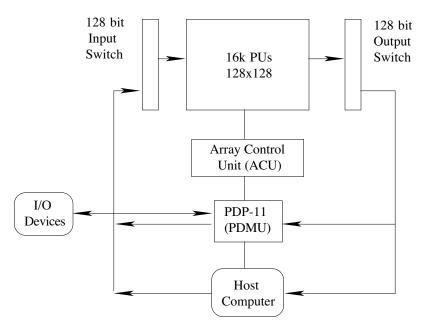

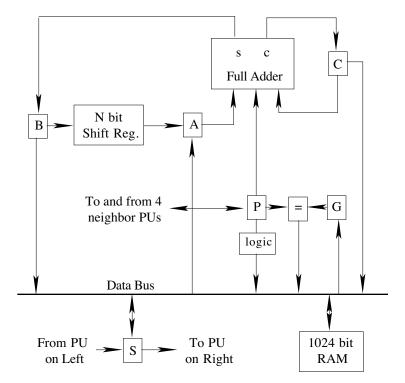

|     | <ul> <li>5 The Hypercube</li> <li>6 Array Processors</li> <li>7 Example: MPP</li> <li>8 Example: The Connection Machine</li> </ul> |                                       | 191 |     |  |

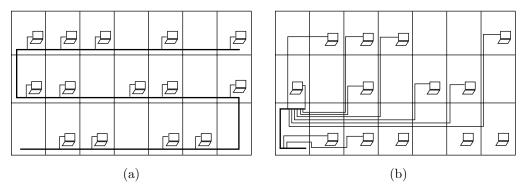

|     |                                                                                                                                    |                                       | 193 |     |  |

|     |                                                                                                                                    |                                       | 195 |     |  |

|     |                                                                                                                                    |                                       | 197 |     |  |

|     | 9                                                                                                                                  | MIMD Computers                        | 199 |     |  |

|     | 10                                                                                                                                 | Parallel Algorithms                   | 200 |     |  |

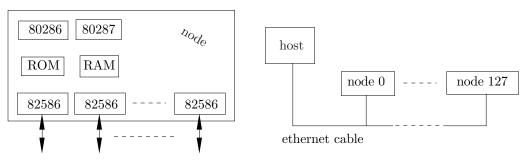

|     | 11                                                                                                                                 | The Intel iPSC/1                      | 202 |     |  |

|     | 12                                                                                                                                 | Vector Processors                     | 204 |     |  |

|     | 13                                                                                                                                 | The Von-Neumann Bottleneck            | 205 |     |  |

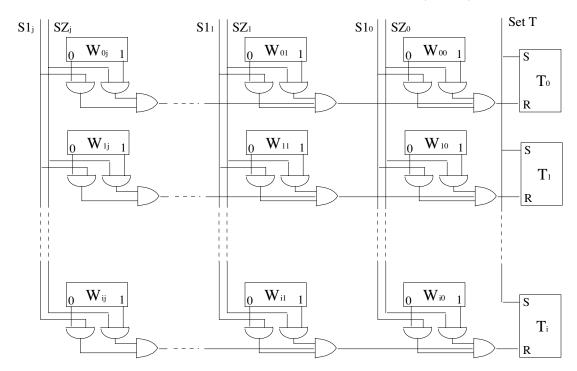

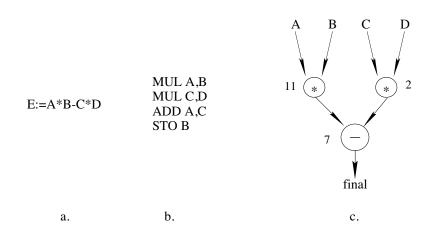

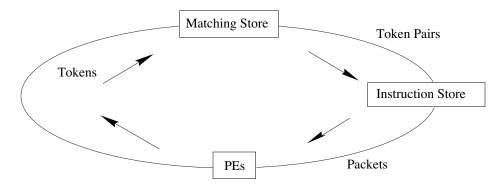

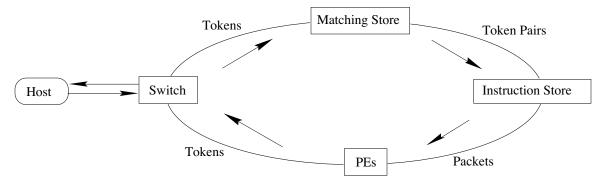

|     | 14                                                                                                                                 | Associative Computers                 | 206 |     |  |

|     | 15                                                                                                                                 | Data Flow Computers                   | 209 |     |  |

| 6.  | Reduced Instruction Set Computers                                                                                                  |                                       |     |     |  |

|     | 1                                                                                                                                  | Reduced and Complex Instruction Sets  | 219 |     |  |

|     | 2                                                                                                                                  | A Short History of RISC               | 221 |     |  |

|     | 3                                                                                                                                  | The RISC I Computer                   | 222 |     |  |

|     | 4                                                                                                                                  | Conclusions                           | 226 |     |  |

| 7.  | Digi                                                                                                                               | tal Devices                           |     | 227 |  |

|     | 1                                                                                                                                  | Combinational and Sequential Devices  | 228 |     |  |

|     | 2                                                                                                                                  | Multivibrators                        | 228 |     |  |

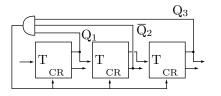

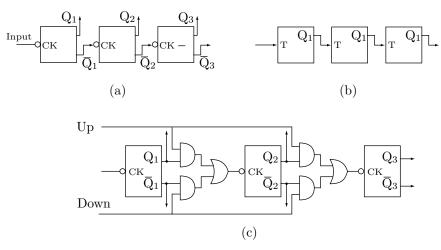

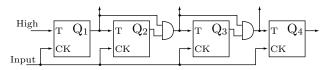

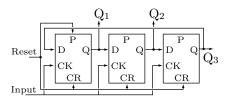

|     | 3                                                                                                                                  | Counters                              | 232 |     |  |

|     | 4                                                                                                                                  | Registers                             | 236 |     |  |

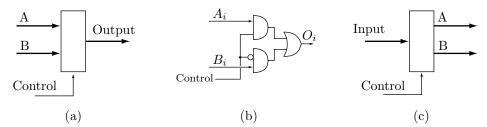

|     | 5                                                                                                                                  | Multiplexors                          | 236 |     |  |

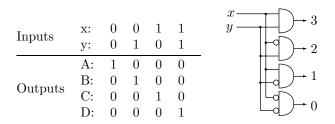

|     | 6                                                                                                                                  | Decoders                              | 237 |     |  |

|     | 7                                                                                                                                  | Encoders                              | 237 |     |  |

| 8.  | The                                                                                                                                | The Memory                            |     |     |  |

|     | 1                                                                                                                                  | A Glossary of Memory Terms            | 241 |     |  |

|     | 2                                                                                                                                  | Static RAM                            | 242 |     |  |

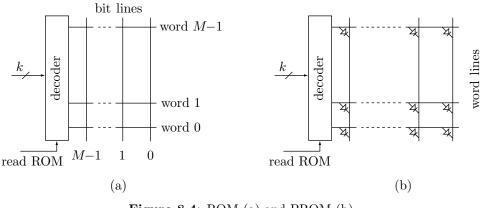

|     | 3                                                                                                                                  | ROM                                   | 243 |     |  |

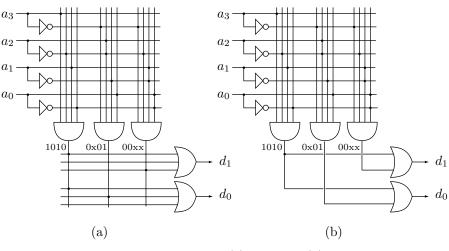

|     | 4                                                                                                                                  | PLA                                   | 245 |     |  |

| 9.  | The ALU                                                                                                                            |                                       |     |     |  |

|     | 1                                                                                                                                  | Integer Addition and Subtraction      | 247 |     |  |

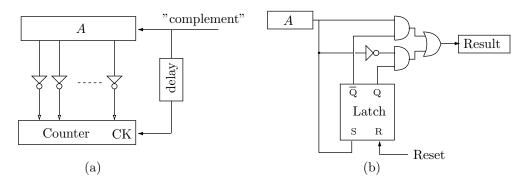

|     | 2                                                                                                                                  | The Accumulator                       | 250 |     |  |

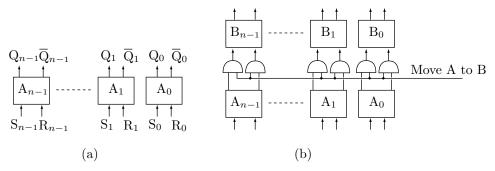

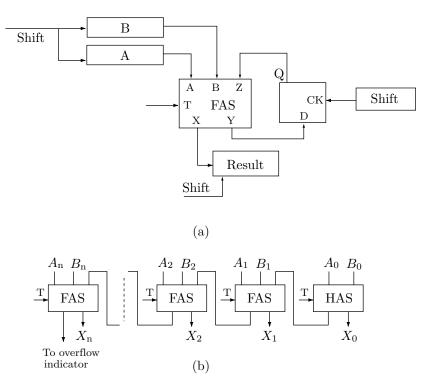

|     | 3                                                                                                                                  | Integer Multiplication                | 252 |     |  |

|     | 4                                                                                                                                  | Integer Division                      | 260 |     |  |

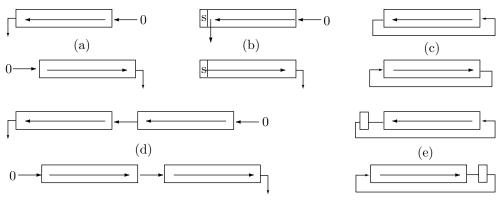

|     | 5                                                                                                                                  | Shifts                                | 261 |     |  |

|     | 6                                                                                                                                  | Comparisons                           | 263 |     |  |

| 10. | Asse                                                                                                                               | emblers                               |     | 267 |  |

|     | 1                                                                                                                                  | Introduction                          | 267 |     |  |

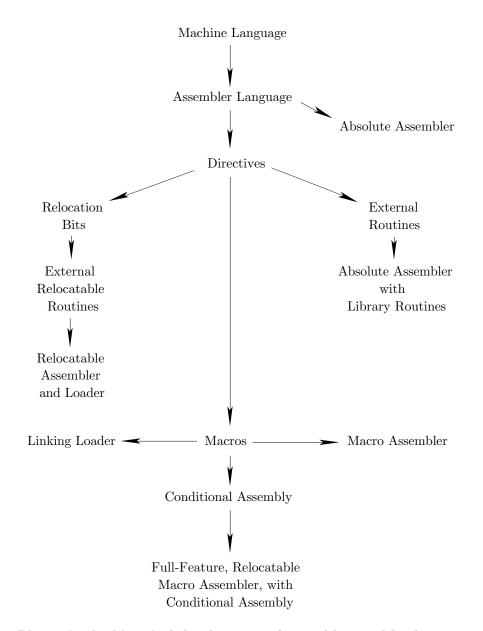

|     | 2                                                                                                                                  | A Short History of Assemblers         | 270 |     |  |

|     | 3                                                                                                                                  | Types of Assemblers and Loaders       | 272 |     |  |

|     | 4                                                                                                                                  | Assembler Operation                   | 272 |     |  |

|     | 5                                                                                                                                  | The Two-Pass Assembler                | 276 |     |  |

|     | 6                                                                                                                                  | The One-Pass Assembler                | 280 |     |  |

|     | 7                                                                                                                                  | Absolute and Relocatable Object Files | 283 |     |  |

|     | 8                                                                                                                                  | Absolute and Rel. Address Expressions | 286 |     |  |

|     | 9                                                                                                                                  | Local Labels                          | 288 |     |  |

|     | 10                                                                                                                                 | Multiple Location Counters            | 289 |     |  |

|     | 11                                                                                                                                 | Literals                              | 293 |     |  |

|     | 12                                                                                                                                 | Attributes of Symbols                 | 294 |     |  |

|     | $13^{}$                                                                                                                            | Assembly-Time Errors                  | 295 |     |  |

|     | 14                                                                                                                                 | The Symbol Table                      | 296 |     |  |

|     |                                                                                                                                    | v                                     |     |     |  |

Contents

| 1     | Introduction                   | 301 |  |  |  |

|-------|--------------------------------|-----|--|--|--|

| 2     | Macro Parameters               | 304 |  |  |  |

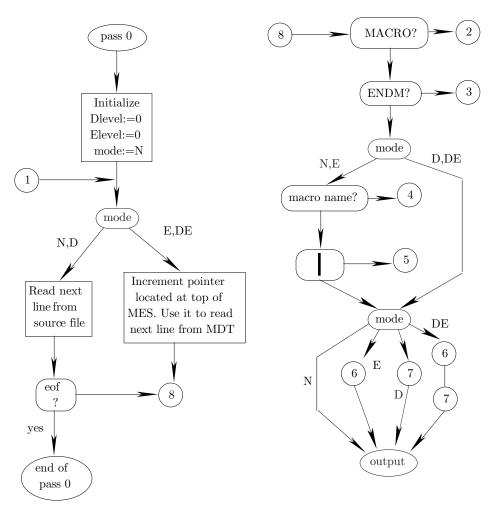

| 3     | Pass 0                         | 308 |  |  |  |

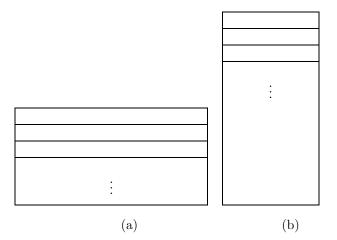

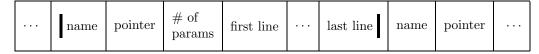

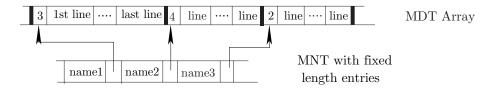

| 4     | MDT Organization               | 310 |  |  |  |

| 5     | Other Features of Macros       | 311 |  |  |  |

| 6     | Nested Macros                  | 315 |  |  |  |

| 7     | Recursive Macros               | 318 |  |  |  |

| 8     | Conditional Assembly           | 318 |  |  |  |

| 9     | Nested Macro Definition        | 324 |  |  |  |

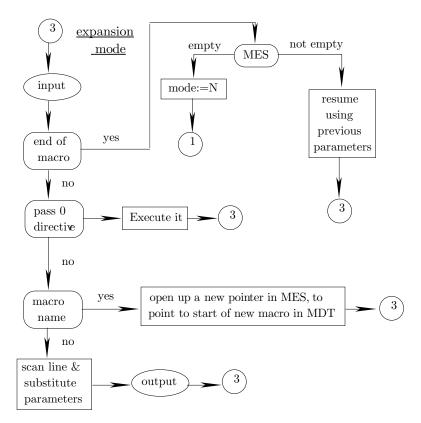

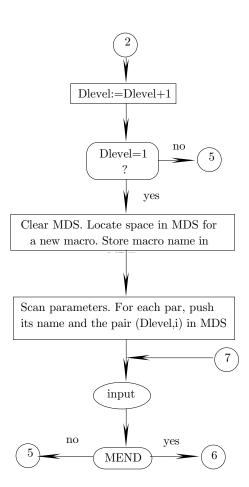

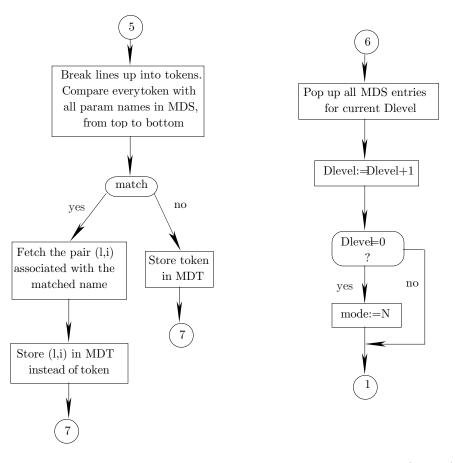

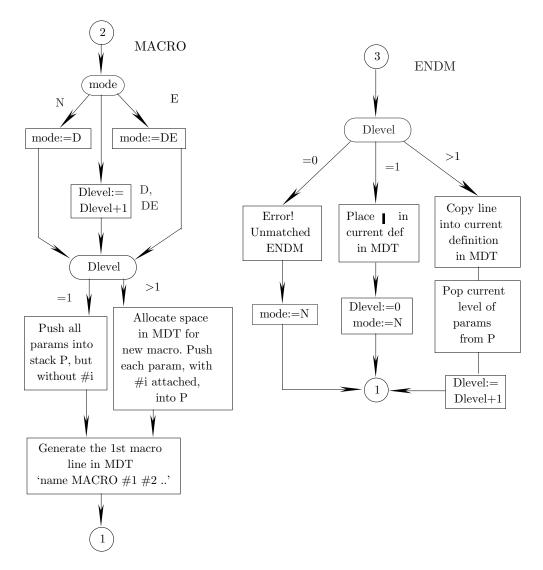

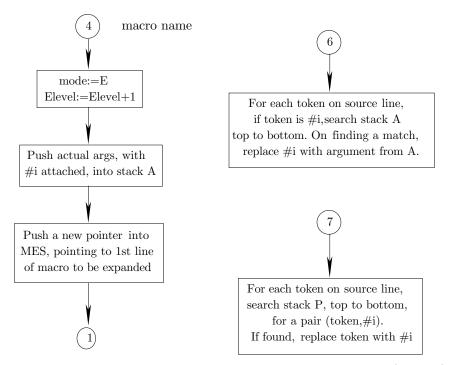

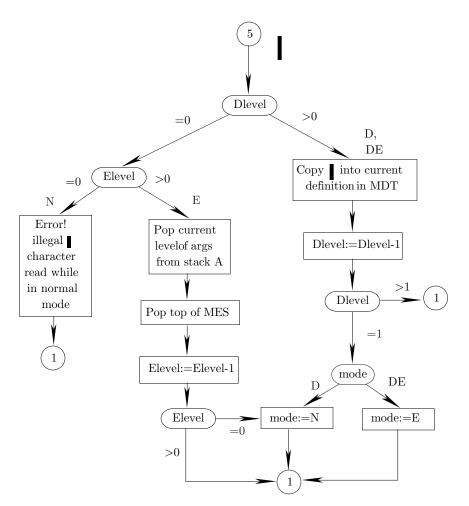

| 10    | Summary of Pass 0              | 334 |  |  |  |

| . His | History of Computers           |     |  |  |  |

| 1     | A Brief History of Computers   | 337 |  |  |  |

| 2     | First Generation. Vacuum Tubes | 340 |  |  |  |

| 3     | Second Generation: Transistors | 342 |  |  |  |

| 4     | Third Generation: ICs          | 342 |  |  |  |

| 5     | Later Developments             | 342 |  |  |  |

| . Un  | icode                          |     |  |  |  |

| . The | The Compact Disc               |     |  |  |  |

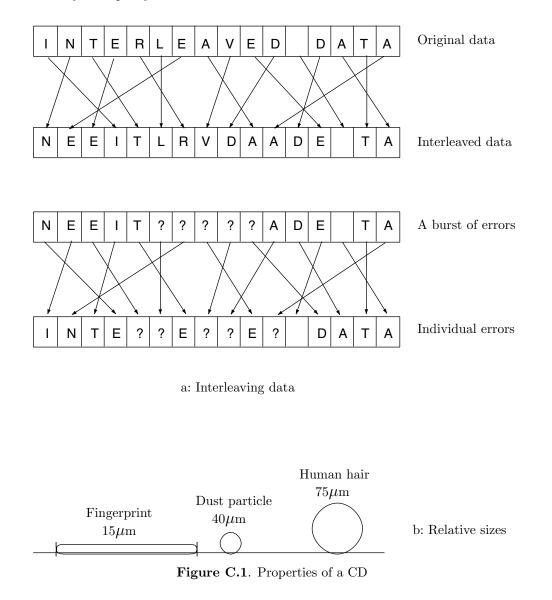

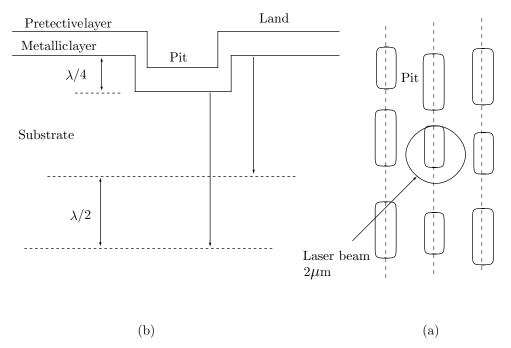

| 1     | Capacity                       | 353 |  |  |  |

| 2     | Description                    | 354 |  |  |  |

| 3     | Error-Correction               | 354 |  |  |  |

| 4     | Encoding                       | 356 |  |  |  |

| 5     | The Subcode                    | 357 |  |  |  |

| 6     | Data Readout                   | 357 |  |  |  |

| 7     | Fabrication                    | 357 |  |  |  |

| 8     | The CD-ROM Format              | 358 |  |  |  |

| 9     | Recordable CDs (CD-R)          | 359 |  |  |  |

| 10    | Summary                        | 359 |  |  |  |

| 11    | DVD                            | 360 |  |  |  |

| . ISC | ISO Country Codes              |     |  |  |  |

| Rei   | References                     |     |  |  |  |

| An    | Answers to Exercises           |     |  |  |  |

| Ind   | Index                          |     |  |  |  |

| ing   |                                |     |  |  |  |

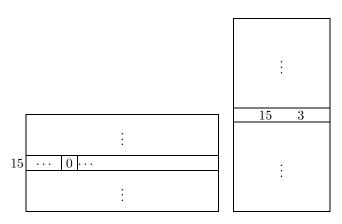

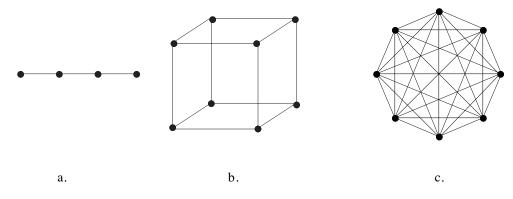

Perhaps the main reason why computers are so prevalent in modern life is the fact that a single computer can perform a wide variety of tasks and can solve problems in many fields. The reason for that is that anything that the computer does is driven by software. When we want to use a computer, we have to write a program (or use an existing program). Without a program, the computer can do nothing. With the right program, the computer can perform the right task. Therefore, the most important computer feature is the way it executes a program. The bulk of this chapter is thus devoted to the execution of instructions. The part of the computer that's responsible for instruction execution is called the control unit (CU).

This chapter starts with a discussion of the control unit and its operations. This topic is illustrated by several examples of instruction execution. A simple register transfer notation is used to describe the execution of instructions by the control unit. The execution of many instructions requires a memory access, so the next topic of this chapter is the memory unit, its main features and operations. The discussion concentrates on the interface between memory and the control unit, and the way the control unit performs memory operations. The internal operations of the memory unit itself are not discussed.

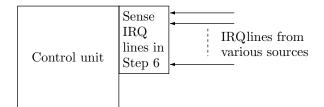

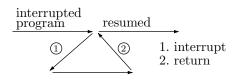

The important concept of *interrupts* is treated in Section 1.7, because the hardware aspects of interrupts are part of the control unit. Vectored interrupts are explained, followed by the two main problems of a multi-interrupt system, namely simultaneous interrupts (and interrupt priorities), and nested interrupts (and interrupt enabling/disabling). The section concludes with a discussion of software interrupts and their applications to time slices and privileged instructions.

Section 1.8 discusses I/O interrupts. Notice that input/output is fully treated in Chapter 3.

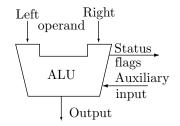

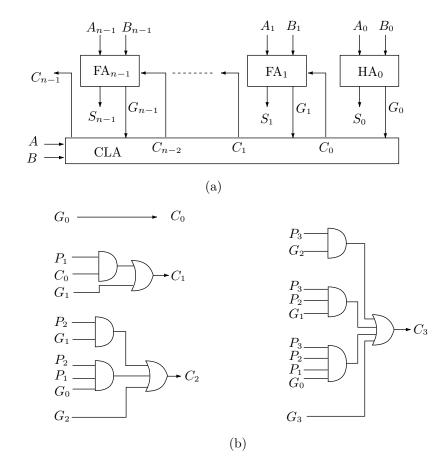

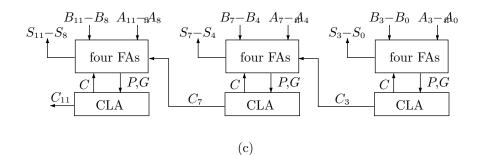

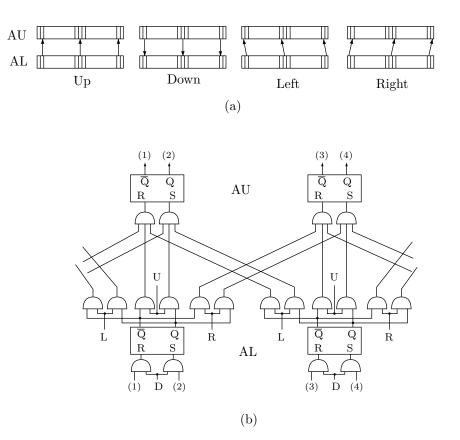

Section 1.10 is a short introduction to the ALU and its operations. Simple circuits for adding integers are described. Chapter 9 is a detailed treatment of many ALU circuits.

# 1.1 Terminology

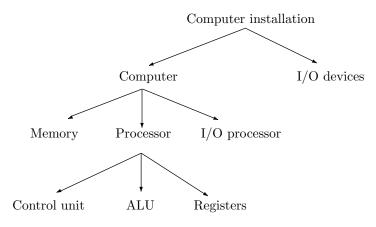

Computers consist of many components so, in order to concentrate our discussion, standard terminology is needed. The most general concept discussed here is that of a *computer installation*. An installation consists of a computer (or several computers), I/O devices such as modems, printers, and disk drives, personnel, and secondary features such as air conditioning, cables, and raised floors. Notice that a personal computer can also be considered a computer installation since it includes I/O devices.

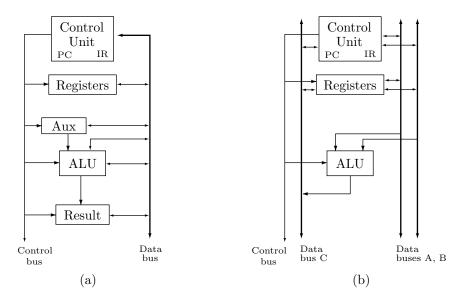

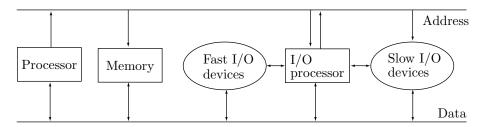

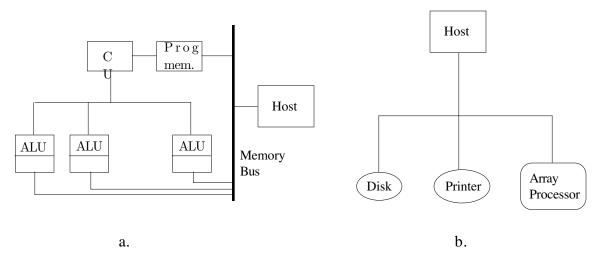

From the point of view of organization, the computer is divided into three components, the processor, the memory, and the I/O processor. The memory is a passive component. It simply stores the information written in it. The function of the I/O processor is to interface the computer to the outside world. Advanced I/O processors can perform the actual input and output operations, thereby releasing the processor from this slow task. The processor (or *central processing unit*, CPU) is the main part of the computer. Its task is to execute the program instruction by instruction. The processor itself is functionally divided into three components, the control unit (CU), the arithmetic and logical unit (ALU), and the registers. The registers

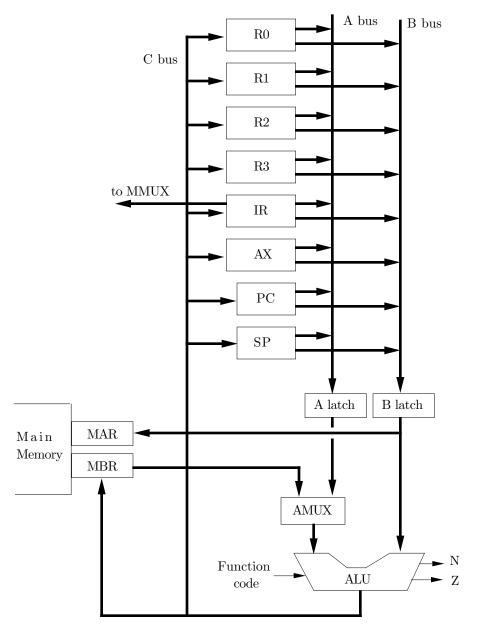

are fast storage units, where a few pieces of information can be stored temporarily until they are needed by the program. The ALU and the registers are sometimes combined and are called the RALU. Figure 1.1 illustrates the relations between these components.

Figure 1.1: Basic computer terminology

• Exercise 1.1: Why is input/output a slow task?

# 1.2 The Control Unit

The computer is an information processing machine and the processor (CPU) is that part of the computer where information is processed. More specifically, the processor executes the program.

The main feature of the computer, the feature that makes it so different from other machines, is the *internal control*. The computer is controlled by a *program*, which specifies the operations to be performed. The program is located in memory, outside the processor, and the processor executes the program by reading (fetching) it from memory, instruction by instruction, and executing each instruction. This task is performed mainly by the control unit (CU), which uses the ALU and the registers as tools. The ALU is that part of the processor where operations are performed on numbers. The registers, as mentioned earlier, are fast, temporary storage.

The control unit is the main part of the processor. It performs its task by repeatedly cycling through the following steps:

- 1. Read (fetch) the next instruction from memory.

- 2. Examine the instruction to determine what it is and to find any possible errors.

- 3. Execute the instruction.

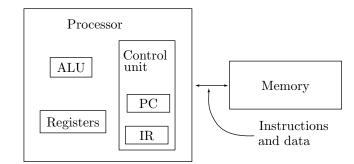

These steps are known as the fetch-execute cycle. In order to read the next instruction from memory, the control unit needs to know the location (memory address) of the instruction. This address is kept in a special register called the *program counter* (PC). The PC is a special register and is normally located in the control unit. It always contains the address of the *next* instruction, not the current one. When the next instruction is fetched, it is stored in the *instruction register* (IR), another special-purpose register, that always contains the current instruction. Note that as soon as the next instruction is fetched and is stored in the IR it becomes the *current* instruction (Figure 1.2).

• Exercise 1.2: Can the PC be one of the general-purpose registers (GPRs)?

The fetch-execute cycle can now be rewritten as:

- 1. Read the instruction that's pointed to by the PC from memory and move it into the IR.

- 2. Increment the PC.

- 3. Decode the instruction in the IR.

4. If the instruction has to read an operand from memory, calculate the operand's address (this is called the *effective address*, or EA) and read the operand from memory.

5. Execute the current instruction from the IR.

Figure 1.2: The main components used in the fetch-execute cycle

Step 2 is important since the PC should always point to the next instruction, not to the current one (the reason for this is discussed below). The PC is incremented by the size of the instruction (measured in words). In modern computers, instructions have different sizes. The control unit therefore has to determine the size of the instruction, make sure that all parts of the instruction have been fetched, then increment the PC. Step 2 is, therefore, not as simple as it sounds, and it is combined with Step 3. Instruction sizes are discussed in Section 2.1.

In Step 3, the instruction is examined (decoded) to determine what it is and how it is executed. Various errors can be detected at this step, and if an error is detected, the control unit does not proceed to Step 4 but instead generates an *interrupt* (Section 1.7).

## • Exercise 1.3: What errors can be detected when an instruction is decoded?

Step 4 is executed only if the instruction needs to read an operand from memory or if it uses an addressing mode. Addressing modes are discussed in detail in Section 2.3.

In Step 5, the control unit executes the instruction by sending signals (control signals) to the ALU, to the memory, and to other parts of the computer. Step 5 is the most complex part of the control unit, since the instructions are different, and each should be executed differently. The control unit has a different circuit for executing each instruction and, since a modern computer might have more than 100 different instructions, the control unit is a large, complex circuit.

On considering the steps above, the reader may wonder why they are arranged in this order. Specifically, why does the control unit perform *fetch—increment PC—execute*, rather than *fetch—execute—increment PC*. In fact, the latter sequence may seem more natural to most.

It turns out that for most instructions, the two sequences above are identical and the control unit can use any of them. However, there is one group of instructions, those affecting the flow of control, where the *fetch—increment—execute* sequence is the only one that works.

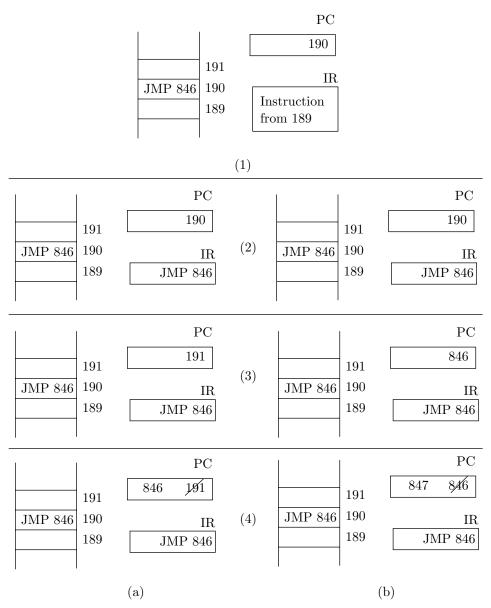

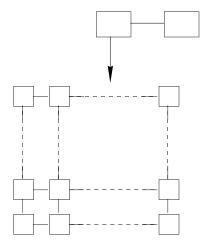

Such instructions are the various jumps and branches. They are used to change the normal flow of control, the way execution proceeds within a program, and they themselves are very easy to execute. Executing an instruction such as JMP 846 is done simply by resetting the PC to 846 (to the jump address). Since the PC is supposed to point to the next instruction, resetting the PC guarantees that the next instruction will be fetched from location 846. Figure 1.3 compares the operations of the control unit in both the *fetch increment*—*execute* (part a) and the *fetch*—*execute*—*increment* (part b) sequences. It is easy to see that the latter sequence ends up with the PC being reset to address 847, which is obviously wrong.

#### • Exercise 1.4: What other instructions change the flow of control?

The upper part of Figure 1.3 shows memory locations 189–191 with the JUMP instruction stored in location 190. The PC contains 190, so the instruction at memory location 190 is the next one, implying that the current instruction is the one at location 189. In part (a2) the instruction from 190 has been fetched into the IR. In (a3), the PC is incremented to point to the next instruction, the one in location 191. In (a4), the instruction in the IR is executed by resetting the PC. It is reset to the jump address, 846.

In parts (b2), (b3), and (b4), the JUMP instruction is fetched, it is executed by resetting the PC to 846, and, finally, the PC is incremented to 847, which is wrong.

Figure 1.3: Two alternative fetch-execute sequences

# 1.2.1 Control Unit Start and Stop

How does the fetch-execute cycle start? It starts as soon as power to the computer is turned on, which is why it is important to make sure that the PC is set to the correct value as soon as the computer is started. This is done by a special circuit that's invoked when power is turned on (and also every time the computer is reset). The problem is that when the computer is turned on there is nothing in memory, since no program has been written or compiled yet. To what address should this circuit set the PC?

The answer requires an understanding of the interaction between the user (a person), the operating system (a piece of software) and the control unit (hardware). The operating system is a program (rather, a set of programs) whose task is to service the user (in a multiuser computer, the operating system also supervises the users). For example, the various compilers are part of the operating system and they, of course, provide an important service. When a computer is manufactured, a small part of the operating system, called the resident, is permanently written into the lowest area of the computer's memory. The resident (actually, its first part, the *bootstrap loader*) is the first program that's executed each time the

#### 1.3 The Memory

computer is turned on or is reset. (See the discussion of bootstrapping in Section 1.3.1.)

Here is a summary of what happens when the computer is started. The special circuit resets the PC to the start address of the resident part of the operating system (in many computers this is address zero). The control unit starts its cycle, so it fetches and executes instructions from the start of the resident operating system (i.e., the bootstrap loader). This loads the rest of the operating system from disk. The operating system then goes into a loop where it waits for the first user command or action.

- Exercise 1.5: What would happen if the PC does not get set when the computer starts?

- Exercise 1.6: Why not store the entire operating system permanently in memory?

The control unit stops when power to the computer is turned off. This seems a "rough" way to stop the computer, but it makes sense when we consider the way the user, the operating system, and the control unit interact. The user turns the computer on, which starts the resident operating system, which in turn loads the rest of the operating system. The operating system then executes user actions and commands, such as "open a window," "delete a file," "execute a file," "move the cursor," "pull down a menu," "insert a floppy disk into the disk drive," etc. At the end of the session, the user has no more commands/actions, so he turns off the computer. At this point the control unit is still running at full speed, fetching and executing instructions, but we don't mind shutting it off abruptly since those instructions are executed by the operating system while looking for user actions. From the point of view of the user those instructions are effectively useless.

The most important task of the control unit is to execute instructions. However, before this can be discussed in detail, the reader must know something about memory and its operations. The next section discusses memory, and Section 1.4 returns to the control unit and instruction execution.

# 1.3 The Memory

The inner working of computer memories are treated in Chapter 8. This section discusses the basics features of memory, memory operations, and how the control unit executes them. Memory is the second of the three components of the computer. It is used for storage and is therefore a passive component. A piece of data stored in memory is simply saved there and is not operated on. To operate on data, it is necessary to read it from memory and move it to the processor (specifically, to the ALU). Information stored in memory can be either machine instructions or data. Computer memories exhibit the following features:

1. Memory is organized in equal-size units called *words* (or cells). If there are M words in memory, each consisting of N bits, then memory is said to be of size  $M \times N$ . The quantities M (number of words) and N (word size) are two of the most important parameters of the architecture of the computer.

2. Only binary information (bits, zeros and ones) can be stored in a computer memory. In particular, memory cannot be empty. There is no such thing as a blank word in memory. If nothing has been stored in a memory word, it will contain random bits. This is why data has to be stored in memory before it can be read back.

3. There are only two memory operations, read and write. Reading a word from memory brings in a copy of the data. The original stays in the word and may be read again and again. Writing into a word destroys its original data.

4. Memory is accessed on a word basis, so each word should be uniquely identified. This is done by assigning an *address* to each word. Addresses are numeric and run from 0 to M - 1. When memory is accessed, an address has to be specified first. The word associated with that address is accessed, and can either be read from or written to.

It is important to understand that exactly one word can be accessed at any time. It is impossible to read less than a word in memory. To access two words, each has to be accessed individually, a process that requires two separate memory operations. Also, even though modern memories are very fast, a memory unit can only do one thing at a time; it does not operate in parallel (although parallel memories can be made for special applications).

Next, we discuss typical values of M and N. It turns out that certain values are better than others, and an understanding of M and N is important for an overall understanding of computer organization (see also Table 1.4 for standard names of powers of 10).

| Prefix                 | Symbol       | Power      | Value                                         |

|------------------------|--------------|------------|-----------------------------------------------|

| yotta                  | Υ            | $10^{24}$  | $1 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000$ |

| zetta                  | Z            | $10^{21}$  | $1 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000$       |

| exa                    | Ε            | $10^{18}$  | $1 \ 000 \ 000 \ 000 \ 000 \ 000$             |

| peta                   | Р            | $10^{15}$  | $1 \ 000 \ 000 \ 000 \ 000 \ 000$             |

| tera                   | Т            | $10^{12}$  | $1 \ 000 \ 000 \ 000 \ 000$                   |

| $_{ m giga}$           | G            | $10^{9}$   | $1\ 000\ 000\ 000$                            |

| mega                   | Μ            | $10^{6}$   | 1  000  000                                   |

| kilo                   | Κ            | $10^{3}$   | 1000                                          |

| hecto                  | h            | $10^{2}$   | 100                                           |

| deca                   | da           | $10^{1}$   | 10                                            |

| deci                   | d            | $10^{-1}$  | 0.1                                           |

| $\operatorname{centi}$ | с            | $10^{-2}$  | 0.01                                          |

| milli                  | m            | $10^{-3}$  | 0.001                                         |

| micro                  | (mu)         | $10^{-6}$  | 0.000  001                                    |

| nano                   | n            | $10^{-9}$  | $0.000 \ 000 \ 001$                           |

| pico                   | р            | $10^{-12}$ | $0.000\ 000\ 000\ 001$                        |

| femto                  | f            | $10^{-15}$ | $0.000 \ 000 \ 000 \ 001$                     |

| atto                   | a            | $10^{-18}$ | $0.000\ 000\ 000\ 000\ 001$                   |

| zeppo                  | $\mathbf{Z}$ | $10^{-21}$ | $0.000\ 000\ 000\ 000\ 000\ 000\ 001$         |

| yocto                  | У            | $10^{-24}$ | $0.000\ 000\ 000\ 000\ 000\ 000\ 000\ 00$     |

Table 1.4: International standard names of powers of ten

Certain familiar values for M are 8K, 64K, 256K, 1M, (pronounced 'one mega'), and 32M words. The quantity K (the letter K stands for "Kilo") is normally defined as  $10^3 = 1000$  but, since computers use binary numbers, the quantity K that's used in computers is defined as the power of 2 that's nearest 1000. This turns out to be  $2^{10}$  or 1024. Thus, 8K is not 8000 but  $8 \times 2^{10} = 8192$ , and 64K equals  $2^6 \times 2^{10} = 65536$  rather than 64000. Similarly M (Mega) is not defined as a million ( $10^6$ ) but as  $2^{20} = 1024K$ , which is a little more than a million. Notice that M specifies the number of memory words, where a word is N bits long. When N = 8, the word is called a *byte*. However, many modern computers have different values of N.

▶ Exercise 1.7: Express a petabyte (PB) in terms of terabytes (TB), gigabytes (GB), megabytes (MB), kilobytes (KB), bytes, and bits.

Why are such values used for M instead of nice round numbers like 1000, 8000, or 64000? The answer is that 8192 *is* a nice round number, but in binary, not in decimal. It equals  $2^{13}$ . Some of the values mentioned earlier are

$$64K = 64 \cdot K = 2^{6} \cdot 2^{10} = 2^{16}$$

$$256K = 2^{8} \cdot 2^{10} = 2^{18},$$

$$32M = 2^{5} \cdot 2^{20} = 2^{25}.$$

In general, M is always assigned values of the form  $2^j$  for some positive integer j. The reason is that such values make best use of the range of addresses. It turns out that in a memory with  $M = 2^j$  words, every address is a j-bit number, and every j-bit number is a valid address.

To see why this is true, consider the familiar decimal numbers. In a memory with 1000 words, decimal addresses range from 0 to 999. These addresses are therefore 3-(decimal) digit numbers. What's more, *every* 3-digit number is an address in such a memory.

As a simple binary example, consider  $M = 8 = 2^3$ . Binary addresses range from 0 to  $7 = 111_2$  and are therefore 3-bit numbers. Also, every 3-bit number is an address, since  $111_2$  is the largest 3-bit number.

In general, if  $M = 2^{j}$ , addresses vary from 0 to M - 1. But

$$M-1=2^j-1=\underbrace{1\ldots 11}_{j}{}_2,$$

so addresses in such a memory are j-bit numbers.

• Exercise 1.8: How many words are there in a 32M memory?

Old computers typically had memory sizes of 32K or 64K words. The first 8-bit microprocessors also had memories with no more than 64K words. Modern computers, however, both large and small, support much bigger memories and have values of M in the range of 1M to several G (where G, Giga, is defined as  $2^{30}$ ) or even a few T (Tera, or  $2^{40}$ ). Such computers have long addresses, typically in the range of 20 to 40 bits.

It turns out that the address size is an important organizational feature of the computer. Chapter 2 has more to say on the relation between the address size and the design of the instruction set.

The word size, N, also needs to be discussed. Again certain values are preferable while other values make no sense. Many modern computers use N = 8. Such a word is called a *byte*. In general, the value of N is determined by what will be stored in the memory words when the computer is running. Memory words contain either machine instructions or data. Data stored in a word in memory can be of several types (all described in Chapter 2). Two data types, namely characters and decimal digits, are briefly mentioned here in connection with the values of N.

It is possible to store text in memory by assigning a code to each character (letters, digits, and punctuation marks) and storing the codes. The size of the code of a character is one parameter affecting the choice of the word size. Typical character codes have sizes of 7–8 bits. With 7-bit codes, it is possible to code  $2^7 = 128$  characters. With 8-bit codes, the computer can handle a set of up to 256 characters.

It sounds strange, but decimal digits are also stored in memory. We already know that memory can contain only bits, so how can decimal digits be stored in it? The idea is to translate each digit into bits. Since a single decimal digit cannot exceed 9, at most 4 bits are needed. For example, the number 90,762 is translated into the five 4-bit groups 1001, 0000, 0111, 0110, and 0010. Such numbers can be stored in memory and can be operated on, and this fact suggests that the word size should be a multiple of 4. This, combined with the size of a character code, is the reason why the word size of modern computers is a multiple of 8.

It should be mentioned that old computers—most notably the large CDC computers popular in the 1960s and 1970s—had word sizes that were multiples of 6 (Section 3.6). They used 6-bit character codes, allowing for only 64 different characters.

In many modern computers, a memory word consists of several bytes. The individual bytes of a word can be ordered in one of two ways termed *big endian* and *little endian*. The big endian convention arranges the individual bytes of a word such that the last byte (the end) is the biggest (most significant). This is used on processors made by Motorola. Thus, the big endian order is byte0, byte1,... (the least-significant byte is located at the highest address). In little endian, the bytes are arranged such that the last byte (the end) is the "littlest" (least significant). This convention is used on Intel processors. Thus, the little endian order is ..., byte1, byte0 (the least-significant byte is located at the lowest address).

**Exercise 1.9:** Given the four-byte word 00001111|00110101|01011010|00000001, show how it is laid out in memory in big endian and in little endian.

### 1.3.1 Other Features of Memories

First-generation computers had memories made of mercury delay lines or of electromechanical relays. They were bulky, slow, and unreliable. Second-generation computers had magnetic core memories which were smaller, faster, and more reliable. Modern computers use semiconductor memories which are fabricated on integrated circuits, use very little electrical power, and are as reliable as the processor itself (and almost as fast). One important feature of these memories, namely volatility, is discussed in this section.

The two main types of semiconductor memories are ROM and RAM. The acronym ROM stands for "read only memory." The computer can read from this type of memory but cannot write into it. Data can be written in ROM only during its manufacturing process. Some types of ROM can be written to (programmed) using a special device located outside the computer. RAM is Read/Write memory and is of more general use. Incidentally, the name "RAM" stands for "random access memory," but this is an unfortunate name since both ROM and RAM are random access. A better name for RAM would have been RWM (read write memory).

The term "random access" is defined as the case where it takes the same amount of time to read any memory location, regardless of its address. It also takes the same time to write into any location. However, the read and write times are not necessarily the same.

If ROM cannot be written to by the computer, why is it used at all? It turns out that ROM has at least two important applications. It is used for dedicated applications and also for the bootstrap loader.

We are used to computers where different programs are compiled, loaded, and executed all the time. However, many computers spend their "lives" executing the same program over and over. A computer controlling traffic lights, a computer in a microwave oven, and a computer controlling certain operations in a car are typical examples of computers that execute *dedicated applications*. In such computers, the programs should be stored in ROM, since ROM is nonvolatile, meaning it does not lose its content when power is turned off. RAM, on the other hand is volatile.

When a computer is first turned on, there should be a program in memory for the computer to execute. Without such a program it would be impossible to use the computer, since there would be no way to load any programs into memory. This is why computers have a small program, the *bootstrap loader*, in permanent ROM to start things up by loading the rest of the operating system. It should be pointed out that there is another way to bootstrap loader into memory. With volatile semiconductor memories, however, it is more convenient to have a bootstrap ROM.

To increase memory reliability, some computers use a *parity bit* in each memory word. Each time new information is written to the word, the parity bit is updated. Each time the word is read, parity is checked. Since no memory is completely reliable, bits may get corrupted while stored in memory, and it is important to detect such errors.

The idea of a parity bit is to complete the number of 1's in the word to an even number (even parity) or to an odd number (odd parity). For example, suppose the number 010 is written in a 3-bit word and even parity is used. The parity bit should be set by the memory unit to 1, to complete the number of 1's to an even number. When the word is read, the memory unit checks parity by counting the number of 1's. If the number of 1's is odd, memory notifies the processor of the problem by means of an interrupt (Section 1.7). A parity bit is thus a simple device for error detection. However, a single parity bit cannot tell which bit (or bits) is bad.

A single parity bit also cannot detect every possible error. The case where two bits change their values in a memory word cannot be detected by simple parity. There are ways of adding more parity bits to make data more reliable, some of which are discussed in Section 3.9.

• Exercise 1.10: What if the parity bit itself goes bad?

# 1.3.2 Memory Operations

This section treats memory as a black box and does not go into how memory operates internally. We only discuss how memory is accessed by the control unit (later we see that the DMA device can also access memory). As mentioned earlier, there are only two memory operations, namely memory read and memory write. Each operation accesses one word, so at any given time it is only possible to read a word from memory, or to write into a word in memory. When reading from a word, only a copy of the content is read and the original content of the word is not affected. This means that successive reads will read the same data. This behavior is a special case of a general rule that says that when data is moved inside the computer, only a copy is moved and the original is unaffected.

#### • Exercise 1.11: What are exceptions to this rule?

The "memory write" operation, on the other hand, writes new information in the word, erasing its old content. This is the only way to erase information in memory, there being no "erase" operation. After all, a memory word may contain only bits, so there is no such thing as a blank word. As a result, even words that have not been initialized with any information, have something in them, either remnants from an old program, or random bits.

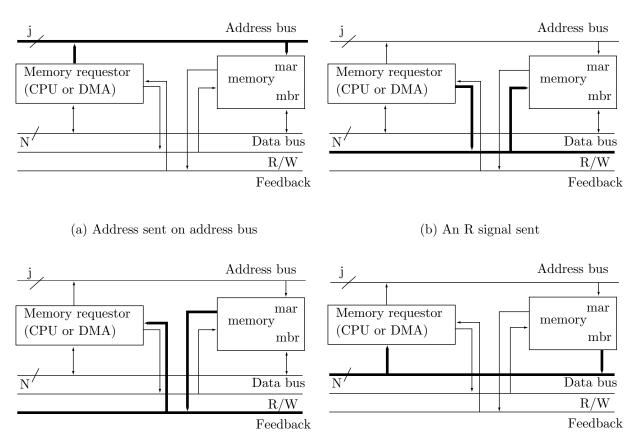

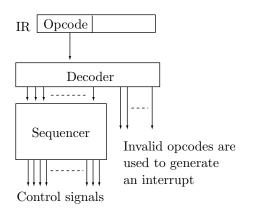

The first step in either memory operation is to send an address to memory. The address identifies the memory word that should be accessed (read from or written into). From that point, the "read" and "write" operations differ. The "memory read" operation consists of the following four steps:

1. Send an address to memory.

2. Send a "read" signal to memory.

3. Wait for memory to complete its internal operations and prepare a copy of the data to be read.

4. Move the content from memory to where it should go.

The address is sent, in Step 1, to a special register called the *memory address register* (MAR). The MAR is a special register in the sense that each time it is accessed from the outside, memory senses it and considers the new content of the MAR an address. The "read" signal in Step 2 is necessary because there can be two operations, read and write. Step 3 is unfortunate—since the control unit has to idle during this step—but it is unavoidable, because memory operates at a finite speed and it is slower than the processor. During this step, the data is moved by memory into a special register called the *memory buffer register* (MBR). In Step 4, the MBR is moved to the processor and can be stored in any of its three components, namely the control unit, the ALU, or the registers.

The four steps above can now be written as follows:

1. MAR $\leftarrow$ Address.

2. "R"

3. Wait.

4. Destination  $\leftarrow$  MBR.

The time it takes to complete these four steps is called the *memory read cycle time*, since it is the minimum time between the start of one memory read and the start of the next memory operation. The time it takes to complete the first three steps is called the *memory read access time*, since this is the time memory is actually busy with the read operation. There are, of course, also a *memory write cycle time* and a *memory write access time*, which may be different from the memory read times.

How long is the wait time in Step 3? In modern semiconductor memories, this time is about 50–100 nanoseconds long, where a nanosecond (ns) is defined as  $10^{-9}$  of a second, or one thousandth of a microsecond. These are incredibly short times, considering that even light, traveling at about 186,000 miles/s, advances only about a foot in one nanosecond! Yet memory is accessed so often that the wait times add up and can count for a significant percentage of the total execution time consumed by a program.

The signals needed to perform a memory access are normally sent by the control unit. Section 3.4 shows that the DMA device can also send such signals. Thus, the circuit that performs a memory access is called the *memory requestor*. The requestor has to know how long to wait in Step 3, and this may not be simple. The computer owner may physically replace some memory chips in the computer, and it is practically impossible to change the wait time in the processor each time memory is replaced. Also, a computer may have several memory chips, some faster than others. A simple solution is to let memory send a feedback signal, announcing to the outside world that the wait period is over. The memory requestor should proceed with Step 4 upon receiving that signal.

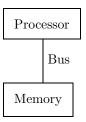

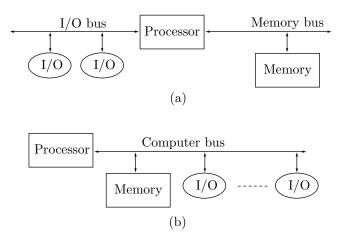

Figure 1.5 summarizes the steps of a memory read. It shows how the signals move between the CPU and memory on groups of wires called *buses*. The bus is an important architectural concept that has not been mentioned yet.

A computer bus is a group of wires (or printed connections) carrying signals of the same type. Three buses are shown in Figure 1.5. The address bus, carrying the j bits of an address, the data bus, carrying the N bits of a word or a register, and the control bus, with R, W, and Feedback lines. Computer buses are discussed in Chapter 3.

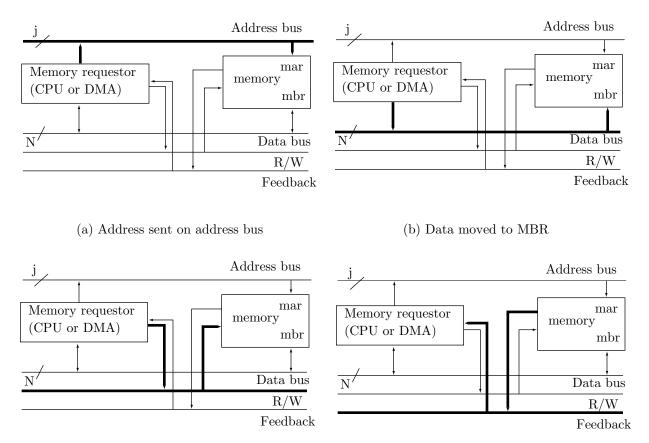

Memory write is, of course, different from memory read, but not significantly. The steps are:

1. MAR←address.

2. MBR←data.

3. "W"

4. wait.

The steps are different and a "W" (write) signal is necessary. However, the main difference between the read and write sequences is the wait period.

During memory read, the memory requestor must wait. During a memory write, however, since the wait period is the last step, the requestor can—at least in principle—do something else. The idea is that in Step 4, while memory is busy with its internal operations, no new memory access can start. However, If the requestor does not need another memory access, it can continue and can perform an internal operation. For

# The von Neumann Bottleneck

A conventional computer, traditionally called a *von Neumann machine*, consists of an ALU—where numbers are operated on—a control unit, responsible for instruction fetch and execute, and a memory—arranged as a linear array of fixed-size cells or words—where data and instructions are stored.

This is an elegant, powerful, and general-purpose design, which has proved its usefulness countless times in the last fifty years. During that period, however, both designers and users of computers came to realize that the simplicity and generality of the von Neumann machine are not only advantages but are also the cause of the limitations of the design. We now recognize two specific disadvantages of the von Neumann machine. The first is its excessive dependence on addresses; the second is the fact that the program control is sequential and centralized.

Here we discuss the first point, traditionally called the *von Neumann bottleneck* (Section 5.13). It is a result of the fact that every memory access must start by sending an address to memory. We can view the computer as consisting of two components, the processor and the memory, connected by a single communications channel, the memory bus. At any given time, a single word can be sent, on the bus, between the processor and memory, and it must be preceded by its address, sent on the same bus. This means that in order to read or write a piece of data from memory, the processor has first to obtain the address of that data, then send the address to memory. The address can be obtained in three different ways:

1. It can come from a register in the processor.

2. It can be part of an instruction. In that case, the instruction should first be fetched from memory, which means that *its address* has to be sent to memory through the bus.

3. It can be obtained as a result of some calculations. In this case, *several* instructions have to be fetched and executed, which implies that *their addresses* have to be pushed through the same bus, which now justifies the name *von Neumann bottleneck*. Note also that the program itself has to be fetched—instruction by instruction—from memory, and an address has to precede each such fetch.

As a result, we can now picture the von Neumann machine as a device that spends a large part of its time pumping addresses and data through the single bus connecting the processor and memory. Not a very efficient picture.

The realization that the von Neumann bottleneck places a limitation on the performance of present computers has led many designers to search for computer architectures that minimize the number of addresses, or that completely eliminate addresses. Two interesting approaches are the concepts of *associative computers* (Section 5.14) and *data flow computers* (Section 5.15), that are discussed in computer architecture texts and have had limited applications in practice.

(c) Feedback from memory

(d) Data moved from memory

Figure 1.5: Details of memory read

example, suppose that the control unit has initiated a memory write. During Step 4, the control unit can perform a register shift, which is an internal operation and does not involve memory.

Figure 1.6 summarizes the steps of a memory write operation.

With this knowledge of the memory unit and its two operations, we are now ready to look at the details of how the control unit fetches and executes instructions.

# **1.4 Instruction Execution**

Fetching an instruction is a "memory read" operation. All instructions are fetched from memory in the same way, the only difference being the size of the instruction. In modern computers, some instructions are long. They occupy more than one memory word, and therefore have to be fetched in two or even three steps. In supercomputers, memory words are long (typically 64 bits each) and instructions are packed several to a word. In such a machine, reading a word from memory fetches several instructions, of which only the first can be immediately moved to the IR and executed. The rest are stored in an instruction buffer, waiting to be executed.

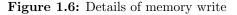

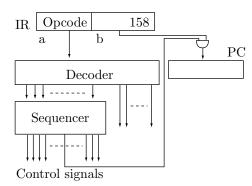

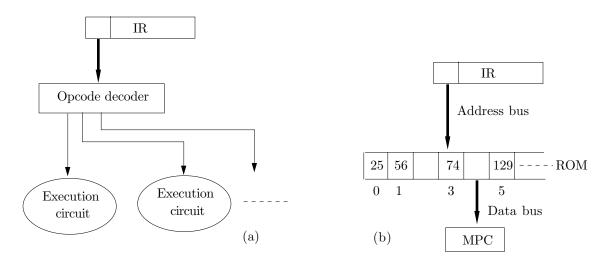

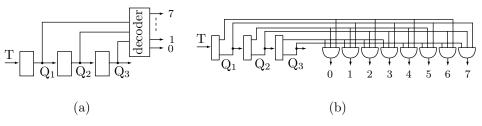

Decoding the current instruction, in Step 3, is done by passing the opcode through a decoder (Figure 1.7).

The decoder outputs are connected to the various execution circuits of the control unit and each output activates "its" execution circuit to execute an instruction. An execution circuit executes an instruction by generating a sequence of control signals that are sent to various parts of the computer. It should also be mentioned that in modern computers, opcodes have different lengths, so the control unit has to figure out the length of the opcode before it can decode it. Variable size opcodes are discussed in Section 2.2.

The opcode decoder is also the point where invalid opcodes are detected. Most computers have several

(c) A W signal sent

(d) Feedback from memory

Figure 1.7: Decoding the opcode

unused opcodes (to be used in future versions of the machine), and as a result, some of the decoder outputs do not go to any execution units. Those outputs are connected together and, when any of them becomes active, that signal is used to generate an interrupt.

Instruction execution, however, is different from fetching and decoding and is much more complex than the operations in Steps 1–4 of the control unit cycle. Modern computers can have a large instruction set with as many as 200–300 instructions. Some instructions are similar and are executed in very similar ways.

#### 1.4 Instruction Execution

Others are very different and are executed in completely different ways. In general, the control unit has to treat each instruction individually, and therefore has to contain a description of the execution of each instruction. The part of the control unit containing those descriptions is called the *sequencer*. This is the collection of all the execution circuits.

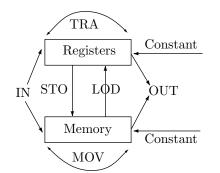

The sequencer executes an instruction by sending a sequence of control signals to the different parts of the computer. Most of those signals move data from one location to another. They perform *register transfers*. Other signals trigger parts of the computer to perform certain tasks. For example, a "read" signal sent by the sequencer to memory, triggers memory to start a "read" operation. A "shift" signal sent to the ALU triggers it to start a shift operation. The examples below list the control signals sent by the control unit for the execution of various instructions.

#### The Three Steps

Following are a few examples of the execution sequences for certain common instructions. Notice that each example is presented in **three steps**. We first show how the programmer writes the instruction in assembler language (the precise notation depends, of course, on the particular assembler used; the notation used here is "generic"). Next, we show how the assembler assembles the instruction. The result is several numbers that together constitute a machine instruction (they are the *fields* of the instruction). The third step is the actual execution. It is important to realize that the three steps are distinct. They are performed by different entities and at different times. The first step is done by the programmer (a person) at the time the program is written. The second step is performed by the assembler (software) at assembly time, where instructions are assembled but not executed. The third step is done by the control unit (hardware) at run time (i.e., when the program is executed). However, all three steps are important and should be carefully studied for a complete understanding of the control unit and its operations.

Example 1. JMP 158. The programmer writes the mnemonic JMP and the jump address 158. The

assembler assembles this as the two-field instruction 158. The control unit executes a jump instruction by resetting the PC to the jump address (address 158). Figure 1.8 shows the components involved in executing the instruction.

Figure 1.8: Executing a JMP instruction

It seems that the only operation necessary in this case is  $PC \leftarrow 158$ . This notation seems familiar since it is similar to that used in higher-level languages. In our case, however, this notation indicates operations performed by the control signals, and such operations are simple. A control signal can cause the transfer of register **A** to register **B**, but cannot move a constant to a register. This is why we need to have the jump address in a register. That register is, of course, the IR, where the instruction is located during execution. Since our example instruction has two parts, we assume that the IR is partitioned into two fields a and b such that IR<sub>a</sub> contains the opcode and IR<sub>b</sub> contains the address. The only control signal necessary to execute the instruction can now be written as:  $PC \leftarrow IR_b$ .

# A useful rule

When an instruction is executed by the control unit, it is located in the IR.

Execution follows the fetch and decode steps, so when an instruction is executed, it has already been fetched into the IR and been decoded. When the control unit needs information for executing the instruction, it gets it from the IR, because this is where the instruction is located during execution (some information is obtained from other sources, such as the PC, the SP, and the general-purpose registers, GPRs).

As a result, many of the control signals used by the control unit access the IR.

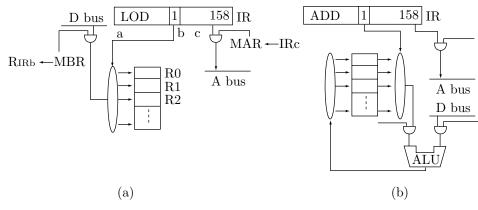

**Example 2.** LOD R1,158. The programmer writes the mnemonic LOD, followed by the two operands (register and address) separated by a comma. The assembler generates the 3-field machine instruction LOD 1 158

List  $\Gamma$  We label these fields a, b, and c (where field  $IR_b$  is the register number and field  $IR_c$  contains the address). This instruction loads the content of memory location 158 into R1 (one of the GPRs, in the processor). Before executing the instruction, the control unit has to calculate the effective address. The way this is done in practice depends on the addressing mode used. In this example we assume that the instruction contains the effective address and that no special addressing mode is used. Executing the instruction involves reading the operand from memory and moving it to the destination register. The steps are:

1. MAR  $\leftarrow$  IR<sub>c</sub> 2. "R" 3. wait 4. R1  $\leftarrow$  MBR

However, Step 4 cannot really be written in this form since these steps should be valid for any LOD instruction. Step 4 should therefore be general. Instead of using the explicit name of the destination register, it should get that name from field c of the IR. We can write this step  $R_{IR_b} \leftarrow MBR$ . The four steps are illustrated in Figure 1.9a.

**Example 3.** ADD R1,158. This is similar to the previous example, and is illustrated in Figure 1.9b. Executing this instruction involves the steps:

Figure 1.9: Executing LOD and ADD

- Read one operand from memory and send it to the ALU.

- Move the other operand from the register to the ALU.

- Send a signal to the ALU to start adding.

- Wait for the ALU to finish.

• Move the result (the sum) from the ALU output to its destination (the register). The control signals are:

1. MAR  $\leftarrow$  IR<sub>c</sub>

- 2. "R"

- 3. wait for memory

- 4. left-ALU $\leftarrow$ MBR

- 5. right-ALU  $\leftarrow R_{IR_{b}}$

- 6. "add"

- 7. wait for the ALU

- 8.  $R_{IR_b} \leftarrow ALU$ -output

Notice the wait in Step 7. The processor is waiting for a feedback signal from the ALU, indicating that the ALU has completed the operation. This is similar to the feedback signal from memory.

This example merits careful study for two reasons. One reason is that it illustrates how the task of executing a typical instruction is divided between the control unit and the ALU. The control unit is responsible for moving data between registers, for sending control signals to the various parts of the computer, and for waiting for feedback signals. The ALU, on the other hand, performs operations on numbers. It does nothing else, nor does it know where the numbers came from or where the result is going to.

The other reason this example is interesting is that many instructions are executed by the control unit in a similar (sometimes almost identical) way. In fact, all the instructions that operate on two numbers fall in this category. Thus, instructions such as SUB R2,268, MUL R3,278, and COMPR R4,288 are executed by the control unit in almost the same way. Those instructions are obviously different, but the differences between them are reflected in the way they are executed by the ALU, not by the control unit. Even many single-operand instructions are executed in a similar way.

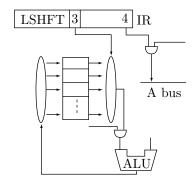

**Example 4.** LSHIFT R3,4. The content of register 3 is to be shifted four positions to the left. The way the programmer writes this instruction is obvious. The assembler assembles it as the 3-field number LSHIFT 3 4

on the shift operation, wait for a feedback signal, and move the result back to the register. The control signals needed are (Figure 1.10):

Figure 1.10: Executing a shift instruction

- 1. left-ALU  $\leftarrow \mathbf{R}_{\mathrm{IR}_b}$

- 2. right-ALU  $\leftarrow$  IR<sub>c</sub>

- 3. ALU-function  $\leftarrow$  'left shift'

- 4. wait for ALU

- 5.  $R_{IR_b} \leftarrow ALU$ -output

Note that the details of this process are transparent to the programmer. The programmer thinks of the shift as taking place in R3. Notice also the similarity between this example and the previous one. The difference between the execution of an add and a shift is in the ALU operation, the signals sent by the control unit are very similar.

**Example 5.** COMPR R4,288. This is a "compare" instruction, comparing its two operands. Writing and assembling this instruction are similar to the previous example. The comparison is done in the ALU and the results (see the discussion of comparisons in Section 2.13.4) are stored by the ALU in the status flags. We can consider the flags part of the ALU, with the control unit having access to them.

The control signals are:

1. MAR  $\leftarrow$  IR<sub>c</sub>

2. 'read'

3. wait

4. left-ALU $\leftarrow$ MBR

5. right-ALU  $\leftarrow R_{IR_b}$

6. ALU-function  $\leftarrow$  'compare'

7. wait for ALU

This should be compared to the control signals issued for executing the ADD instruction above. Note that Step 7 is normally unnecessary. In principle, the control unit should wait for the ALU only if it has to use it again immediately. In most cases, however, the next step of the control unit is to fetch the next instruction, so it does not need to use the ALU for a while. As a result, a sophisticated control unit—of the kind found in modern, fast computers—looks ahead, after Step 6, to see what the next operation is. If the next operation does not use the ALU, Step 7 is skipped. On the other hand, the control unit in a cheap, slow microprocessor—designed for simplicity, not speed—always executes Step 7, regardless of what follows.

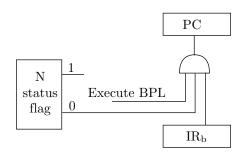

**Example 6.** CALL 248. Calling a procedure is an important programming tool, and every computer includes a CALL instruction in its instruction set. The instruction is executed like a JMP, but the return address is saved. The return address is the address of the instruction following the CALL, so it is found in the PC at the time the CALL is executed. Thus, executing the CALL involves two steps:

1. Save the PC.

2. PC  $\leftarrow$  R<sub>IR<sub>b</sub></sub>.

Where is the PC saved? Most computers use one of three techniques. They save the PC either in a register, in the stack, or in memory.

Saving the PC in a register is the simplest method. The user should specify an available register by writing an instruction such as CALL R5,248, and the control unit saves the PC in R5. The downside of this method is that procedure calls may be nested and there may not be enough available registers to hold all the return addresses at the same time.

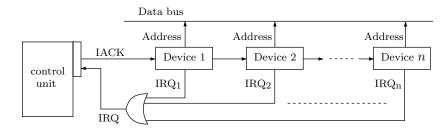

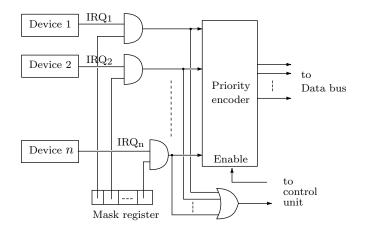

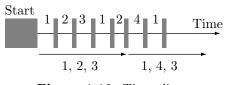

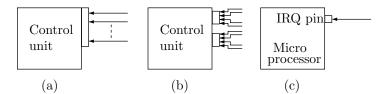

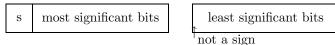

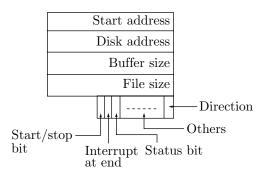

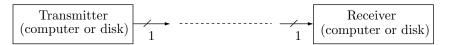

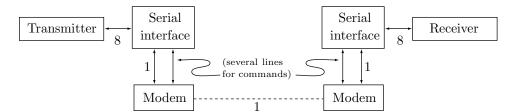

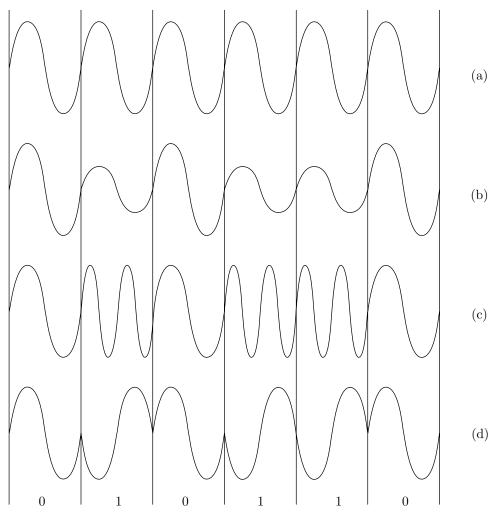

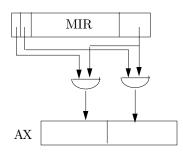

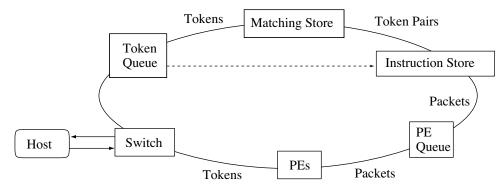

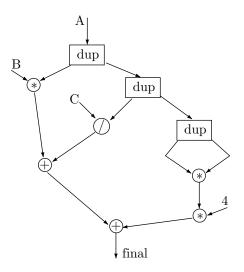

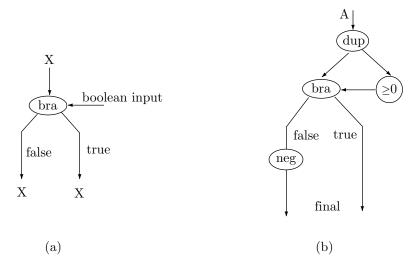

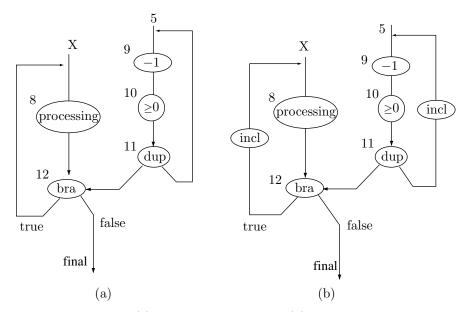

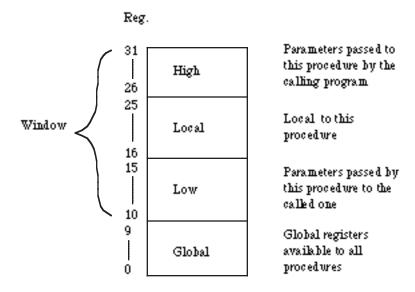

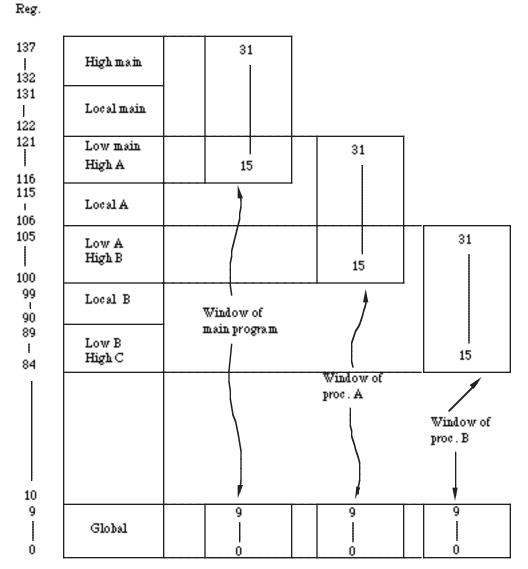

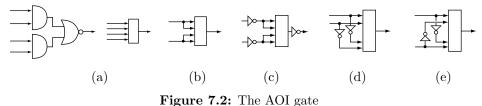

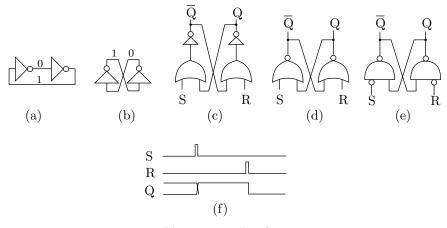

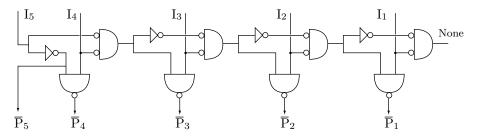

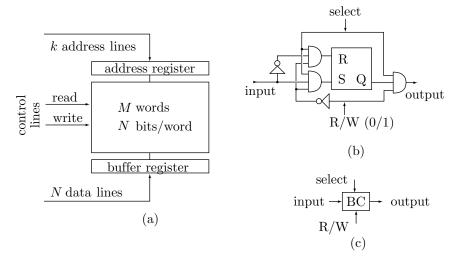

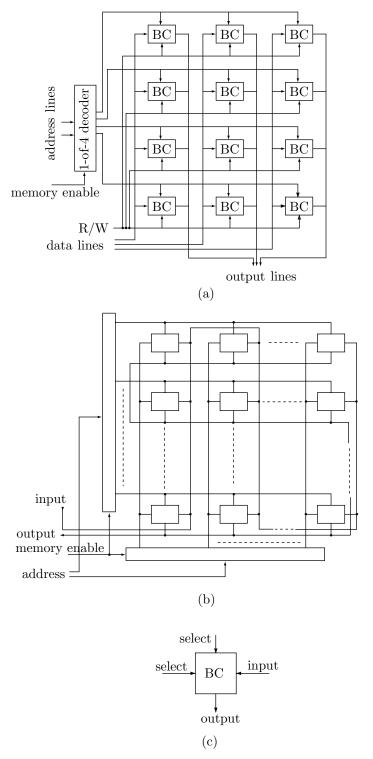

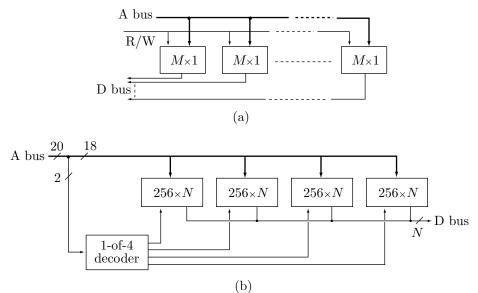

Saving the PC in the stack (stacks are discussed in Section 2.13.5) is a good method since procedure calls are often nested and the *last* procedure to be called is the *first* one to return. This means that the last return address to be saved in the stack is the first one to be used, which conforms to the way a stack is used. Modern computers have stacks and use them extensively. The few old mainframes still in use, generally do not have stacks. Also, some special-purpose computers that have just ROM cannot have a stack.